Операнды – двоичные вектора (коды). У кодов все разряды равнозначны (знаковых разрядов нет).

Необходимо построить комбинационный преобразователь, реализующий набор функций

С(1: n) := А(1: n) * В(1: n),

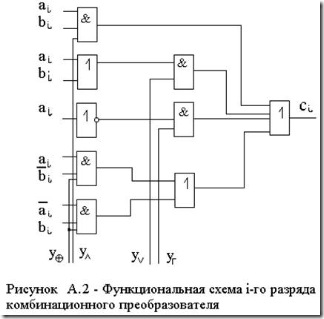

где * - одна из следующих операций над кодами: конъюнкция, дизъюнкция, инверсия, сложение по модулю два (рисунок А.1). Функциональная схема i – го разряда преобразователя представлена на рисунке А.2.

Для выполнения набора функций вида А:=А*В необходимо к построенному преобразователю подключить двухступенчатый регистр (рисунок А.3).

Чтобы реализовать операцию нужно сигнал этой операции yГ закоммутировать на счетный вход соответствующего триггера (i – го разряда регистра А) (рисунок А.4).

Схема, выполняющая микрооперации

yÚ : А := А Ú В и

yÙ : A := A Ù B , приведена на рисунке А.5. Таблица1 описывает операцию дизъюнкции.

| At | Bt | At+1 | |

| 0 | 0 | 0 | |

| 0 | 1 | 1 | |

| 1 | 0 | 1 | |

| 1 | 1 | 1 |

Если yÚ = 1 , то yÙ = 0 (так как две микрооперации не могут выполняться над одним и тем же регистром одновременно), следовательно на R-вход триггера подается ноль (R=0), на S-вход подается bi (S = bi ). Если bi =1, то триггер устанавливается в 1, если bi =0, то триггер хранит свое состояние, т.е. ai. Схема работает в соответствии с таблицей А.1.

Таблица А.2 описывает операцию конъюнкции.

Таблица А.2

| At | Bt | At+1 | |

| 0 | 0 | 0 | |

| 0 | 1 | 0 | |

| 1 | 0 | 0 | |

| 1 | 1 | 1 |

Если yÙ = 1 , то yÚ = 0 (так как две микрооперации не могут выполняться над одним и тем же регистром одновременно), следовательно на S-вход триггера подается ноль (S=0), на R-вход подается (R =

). При

= 0,

= 1, т.е. триггер сбрасывается в ноль. При

=1,

=0, триггер хранит свое состояние , т.е. ai.

На рисунке А.6 изображен i-ый разряд схемы, выполняющей микрооперацию

yÅ : А := А Å В . Таблица А.3 описывает операцию исключающего ИЛИ - сложения по модулю два ( Å).

| At | Bt | At+1 | |

| 0 | 0 | 0 | |

| 0 | 1 | 1 | |

| 1 | 0 | 1 | |

| 1 | 1 | 0 |

При bi =1, ai =1, ai t+1 =0 (триггер переключается);

при bi =1, ai =0, ai t+1 = 1 (триггер переключается);

при bi =0, ai =1, ai t+1 = 1 (триггер не переключается);

при bi =0, ai =0, ai t+1 = 0 (триггер не переключается).

В рассмотренных схемах каждая поразрядная логическая операция реализована одной микрооперацией (выполняется за один такт по соответствующему управляющему сигналу y).

0 коммент.:

Отправить комментарий