Операционные элементы – схемы сравнения

Для подготовки к практическому занятию студентам следует ознакомиться с [1, страница 153-156]. Схемой сравнения называется ОЭ, на котором вычисляется значение отношения между двумя двоичными значениями (словами). Основными отношениями являются выражения и

, которые в зависимости от значений операндов принимают значения ложь (0) или истина (1).

В микропрограммах отношения используются как логические условия и их значения представляются осведомительными сигналами, вырабатываемыми на выходе соответствующих схем сравнения в ОА. В зависимости от типа вычисляемых отношений выделяются :

1) схемы сравнения на равенство (отрицание равнозначности), вычисляющие отношения (

);

2) схемы сравнения на больше (меньше), вычисляющие отношения (

).

Нетрудно убедиться, что схема сравнения на равенство позволяет вычислять отношения и

и схема сравнения на больше позволяет вычислять отношения

,

,

,

. После ознакомления с данной главой объясните почему.

Схемы сравнения на равенство

Сравнение на равенство (отрицание равнозначности) выполняется поразрядно над одноименными разрядами операндов. Операнды равны, если все одноименные разряды операндов имеют одинаковые значения. Операнды не равны, если хотя бы в одном разряде операнды имеют различное значение.

Значение признака равенства i-ых разрядов ( i = 1, 2, …, n) сравниваемых слов и

:

Значение признака неравенства i-ых разрядов сравниваемых слов:

(исключающее или – сложение по модулю 2)

Выше приведены функции в дизъюнктивной канонической форме. Те же функции в конъюнктивной канонической форме:

Признак равенства R двух n-разрядных двоичных слов и

вычисляется как конъюнкция

и признак неравенства Q – как дизъюнкция

Постройте самостоятельно схему сравнения на равенство двух трехразрядных кодов.

Микрооперация сравнения слов на равенство может выполняться на регистре, состоящем из триггеров со счетным входом. Регистр хранит код . По управляющему сигналу

на счетные входы регистра (входы, переключающие триггеры в противоположное состояние при поступлении на них активного уровня сигнала) подается код

, в результате чего регистр

устанавливается в состояние

. Если операнды

и

равны, то регистр устанавливается в состояние

, отмечаемое осведомительным сигналом

, который после выполнения микрооперации

сигнализирует о равенстве значений слов

и

.

Микрооперация сравнения слов на равенство может выполняться на сумматорах, если на момент выполнения микрооперации заблокировать цепи межразрядных переносов. При этом сумматор выполняет сложение операндов по модулю 2 и нулевое значение на выходе сумматора соответствует равенству операндов.

Схемы сравнения на больше (меньше)

Сравнение на больше можно выполнять на сумматоре (или вычитателе) путем определения знака разности

: если разность имеет отрицательный знак, то отношение

истинно, в противном случае оно ложно. Когда необходимость в использовании сумматора отсутствует и требуется вычислять отношения вида

, целесообразно использовать схему сравнения, поскольку она экономичнее сумматора в смысле количества оборудования.

Вычисление отношения между двумя n-разрядными словами

и

сводится к последовательному сравнению разрядов операндов, начиная от старших. Если в

-ом разряде ( i = 1, 2, …, n) имеем

, то отношение

истинно; если

, то отношение

ложно, и, если

или

, то значение отношения определяется путем анализа значений в следующем младшем разряде, а при

отношение ложно. Определим булеву функцию, на основе которой может быть вычислено значение двоичной переменной

, представляющей отношение

. Пусть

- переменная, принимающая значение 1, если факт истинности отношения вытекает из анализа значений в разряде

.

Из правила сравнения следует:

где - признак равенства значений операндов в разрядах от

до

включительно и

- признак равенства

-ых разрядов сравниваемых кодов. Если

, то и

, т.е.

Постройте схему сравнения на больше трехразрядных слов. Оцените максимальную задержку сигнала по отношению к моменту поступления операндов

и

. Если необходимо увеличить быстродействие схемы, то по аналогии со способами ускорения сложения n-разрядная схема делится на группы по k разрядов и организуются обходные цепи передачи сигналов

[1].

Распределители сигналов (тактов)

Распределитель сигналов (РС) – это операционный элемент, вырабатывающий выходные сигналы , принимающие единичные значения в моменты времени

соответственно. Специфика применения распределителей сигналов состоит в том, что они обычно используются для построения управляющих, а не операционных автоматов. На РС удобно строить запоминающую часть автомата, работающего по линейной или легко линеаризуемой микропрограмме. При этом с выходов

РС снимаются сигналы состояний автомата. Выход

может использоваться для перевода (сброса) РС в состояние

. РС может быть переведен в состояние

и специальным управляющим сигналом

. Состояния РС сменяются последовательно (единица переходит на очередной выход) по синхросигналу

(рисунок 9).

Распределитель сигналов может быть реализован как композиция счетчика и дешифратора (рисунок 10,а), а также при помощи регистра сдвига (рисунок 10,б).

Синхросигнал инициирует микрооперацию счета (увеличение значения счетчика на единицу) – рисунок 10,а. Позиционный код состояния счетчика преобразуется дешифратором в унитарный код, расположение единицы в котором соответствует коду в счетчике. Счетчик может быть сброшен в ноль сигналом

или сигналом на

-ом выходе дешифратора. Сигнал, равный дизъюнкции указанных сигналов должен быть подан на вход сброса

счетчика.

Примечание - Если , то после значения

нулевое значение на счетчике устанавливается автоматически.

При реализации РС на основе регистра, хранящего унитарный код (рисунок 10,б), синхросигнал инициирует микрооперацию сдвига в регистре. При этом единица сдвигается на очередной выход регистра, а значение освобождающегося нулевого разряда регистра доопределяется значением

-го разряда (организован циклический сдвиг). Таким образом, обеспечивается автоматический переход регистра из состояния

в состояние

. Управляющий сигнал

позволяет установить РС в состояние

путем загрузки в регистр кода 100…0. Состояния РС иногда называют тактами, а сам РС – распределителем тактов, хотя это название не очень удачно.

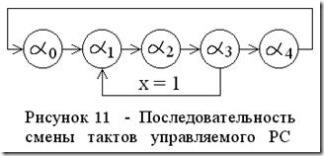

Иногда требуется в зависимости от значения некоторого осведомительного сигнала изменять естественную последовательность смены состояний (тактов). Тогда строят управляемый РС.

Пример 3. Построить схему управляемого распределителя сигналов. Последовательность смены тактов РС задается графом (рисунок 11). Элементный базис – микросхемы К155ИЕ7, К155ИД4.

Схема РС приведена на рисунке 12. Для реализации РС используется режим 3x8 дешифратора К155ИД4 (рассмотрен выше). По очередному синхросигналу код на счетчике К155ИЕ7 увеличивается на 1, а на соответствующем выходе дешифратора появляется уровень логического нуля, т.е. распределитель переходит в следующее состояние

. Объясните нумерацию состояний на выходах дешифратора.

Если осведомительный сигнал , анализируемый в такте

, равен нулю, то за состоянием

следует состояние

(РС следует по большому циклу – рисунок 11). Если осведомительный сигнал

, равен 1, то после состояния

РС должен вернуться в состояние

(РС следует по малому циклу). Для осуществления такого перехода используется режим параллельной загрузки счетчика. На входах параллельной загрузки

фиксируется код состояния

. Сигнал

, поданный на вход

, переводит счетчик в режим параллельной загрузки.

Домножение на синхроимпульс в формуле для используется, чтобы срабатывание асинхронного входа

происходило по синхросигналу. D-триггер (микросхема К155ТМ2) используется для задержки сигнала

. Сигнал

на выходе дешифратора появится (станет равным нулю) по фронту синхроимпульса (т.к. счетчик срабатывает по фронту). Сигнал

на инверсном выходе триггера появится по срезу синхроимпульса (триггер срабатывает по фронту, но на его

-вход подается инверсия синхроимпульса). Появление среза синхроимпульса означает, что текущий синхроимпульс закончился. Следовательно, переключение в состояние

произойдет по фронту следующего синхроимпульса. При отсутствии в схеме триггера РС не будет работать в соответствии с заданной последовательностью смены состояний (рисунок 11), так как состояние

при

исчезнет (объясните почему).

Перевод РС в начальный такт при следовании по большому кругу обеспечивается сигналом с пятого выхода РС (

). Пятое состояние не задействовано в графе смены состояний (рисунок 11). Уровень логического нуля на выходе

появляется по фронту синхроимпульса (поэтому домножение на синхроимпульс в данном случае не нужно).

Примечание - Если в графе РС задействованы все семь состояний, то для управления переходом РС в состояние после состояния

потребуется схема, подобная схеме управления параллельной загрузкой. Если же взять счетчик, считающий от 0 до 7 (а не от 0 до 15 как в рассмотренной схеме), то управлять указанным переходом вообще не нужно (почему?).

РС может быть в любой момент переведен в начальное состояние управляющим сигналом

. С учетом вышесказанного, сигнал перевода PC в состояние

вычисляется по формуле:

Сигнал подается на вход сброса счетчика (вход

).

0 коммент.:

Отправить комментарий