Сумматор – это операционный элемент, предназначенный для выполнения микрооперации сложения чисел. Если операнды и результат сложения представляются в двоичной системе счисления, то сумматор называется двоичным. Сумматоры подразделяются на два типа: комбинационные и накапливающие. Комбинационные сумматоры не содержат запоминающих элементов и реализует микрооперацию сложения в виде C:=A+B. Накапливающие сумматоры содержат регистр, на котором перед началом микрооперации хранится слагаемое и на момент окончания сложения – сумма [1]. Накапливающие сумматоры реализуют микрооперацию сложения в виде С:=С+А.

Структура сумматоров зависит от типа используемых логических и запоминающих элементов и ограничений, налагаемых на длительность микрооперации сложения или количество оборудования.

Операционное устройство может производить арифметические и логические операции в соответствии с заложенной в его основу микропрограммой параллельно, последовательно и параллельно-последовательно. Параллельный способ выполнения операции суммирования двух чисел с фиксированной точкой предполагает, что микрооперация сложения, используемая в микропрограмме суммирования, выполняется над всеми разрядами операндов одновременно (параллельно). Последовательный способ выполнения операции суммирования означает, что соответствующая микрооперация сложения выполняется последовательно над каждым i-ым разрядом суммируемых чисел, начиная с младшего. Поэтому для осуществления сложения двух -разрядных чисел на последовательном двоичном сумматоре потребуется

тактов суммирования (потери времени при этом компенсируются существенной экономией аппаратуры). Компромиссным способом является параллельно-последовательный способ выполнения сложения на двоичном сумматоре. Он предполагает, что микрооперация сложения выполняется над

разрядами суммируемых чисел (т.е.

разрядов суммируются параллельно) ,

,

кратно

. При этом в микропрограмме сложения должна быть предусмотрена микрооперация сдвига регистра, на который записывается сумма, на

разрядов вправо для того, чтобы освободить место для записи суммы следующих по старшинству

разрядов суммируемых слов.

На микрооперации сложения основаны алгоритмы (микропрограммы) выполнения основных арифметических операций в арифметико-логическом устройстве (сложение, вычитание, умножение, деление). Три перечисленных способа выполнения суммирования слов на соответствующих операционных элементах применимы и к выполнению поразрядных логических операций над словами. В соответствии с вышесказанным, арифметико-логические устройства ЭВМ по способу выполнения операций делятся на параллельные, последовательные и параллельно-последовательные.

Параллельный комбинационный сумматор с последовательным переносом. При построении применяется стандартный метод – синтез типового разряда.

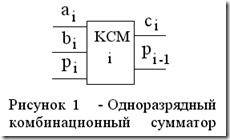

N-разрядный параллельный сумматор с последовательным переносом строится из n одноразрядных комбинационных сумматоров (ОКС). Функция одноразрядного комбинационного сумматора (рисунок 1) представлена в таблице 1.

Таблица 1

| Номер входного набора | Входы | Выходы | |||

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 |

| 2 | 0 | 1 | 0 | 0 | 1 |

| 3 | 0 | 1 | 1 | 1 | 0 |

| 4 | 1 | 0 | 0 | 0 | 1 |

| 5 | 1 | 0 | 1 | 1 | 0 |

| 6 | 1 | 1 | 0 | 1 | 0 |

| 7 | 1 | 1 | 1 | 1 | 1 |

Схема, изображенная на рисунке 1, суммирует ai и bi - значения i-ых разрядов слов А(1:n) и B(1:n) – а также pi - перенос в i-ый разряд суммы из младшего (i+1)-го разряда.

Из таблицы 1 получены следующие функции для определения выходных сигналов ОКС.

Значение i-го разряда суммы:

Значение переноса в старший (i-1)-ый разряд суммы:

По этим функциям строится двухуровневый двоичный одноразрядный комбинационный сумматор с ценой 25 (входов логических элементов) и временем задержки , где

- задержка на логическом элементе.

Цену сумматора можно снизить, если приведенные функции преобразовать в скобочную форму. С этой целью значение суммы представляют функцией , которая строится следующим образом. Полагая,

, мы покрываем единичные значения

на наборах 1, 2, 4. Конституента нуля

обращает указанный терм в 0 на наборе 0. Поскольку

принимает значение 1 на наборе 7, то в функцию

вводится конституента единицы

, соответствующая этому набору.

Окончательно получаем:

По этим выражениям можно построить схему одноразрядного сумматора с ценой С =20. Задержка выработки сигнала суммы с момента подачи входных сигналов ОКС при данной реализации увеличивается. Постройте схему ОКС и определите время задержки.

Схема n-разрядного комбинационного сумматора, построенного на базе ОКС представлена на рисунке 2.

В данном сумматоре сигналы переносов распространяются последовательно от младших разрядов к старшим. По этой причине указанный сумматор называется сумматором с последовательным переносом. Длительность микрооперации сложения определяется суммой времени распространения переносов и времени формирования суммы в одном разряде:

где L – максимальная длина переноса, равная числу соседних разрядов, через которые распространяется сигнал переноса при выполнении сложения, - небольшой запас времени для надежности. При наличии переноса между всеми разрядами сумматора (например, при сложении чисел A=11…11 и B= 00…01 перенос формируется в младшем разряде сумматора и проходит через все остальные разряды)

, и длительность микрооперации сложения составляет

Поскольку фактическое время распространения переноса в схеме рисунка 2 не определяется, то для выполнения микрооперации сложения отводится такт, длительность которого определяется максимальным временем распространения переносов.

Методы ускорения микрооперации сложения

Случай сложения с наличием переносов между всеми разрядами сумматора достаточно маловероятен. Доказано, что в n-разрядном сумматоре, на вход которого поступают слагаемые, равномерно распределенные в интервале , средняя длина самого длинного переноса, затрагивающего группу соседних разрядов, не превышает

. Так, в 32-х разрядном сумматоре переносы пробегают в среднем не более чем через 5 соседних разрядов. Если в сумматор встроить схему, определяющую момент окончания сложения, то время сложения уменьшается в

раз. Сумматор, в котором вырабатывается осведомительный сигнал, отмечающий окончание сложения, называется асинхронным сумматором (схема приведена в [1]).

Еще одним методом уменьшения длительности микрооперации сложения является использование сумматора с групповым переносом. Сумматор делится на групп, каждая из которых содержит

соседних разрядов. В сумматор вводятся цепи, ускоряющие процесс распространения переносов между группами и в пределах каждой группы (схема приведена в [1]).

Комбинационные сумматоры независимо от их внутренней структуры обозначаются на операционных (структурных) схемах как представлено на рисунке 3. Если перенос в младший разряд сумматора всегда равен нулю, то вход на операционных схемах не обозначается. Если перенос из старшего разряда сумматора никак не используется (теряется), то выход

также не обозначается. Выход

может быть использован для увеличения разрядности сумматора (тогда он подается на вход

следующего (старшего) сумматора). При сложении чисел в обратных кодах в сумматоре организуется цепь циклического переноса путем подсоединения выхода

(старшего сумматора, если необходимую разрядность обеспечивают несколько сумматоров) ко входу

(младшего сумматора).

Накапливающие сумматоры

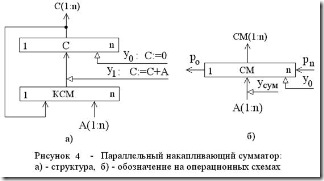

В накапливающем сумматоре значение суммы вычисляется путем сложения предыдущего ее значения со слагаемым, т.е. микрооперация сложения выполняется в виде . Для присваивания сумме начального значения в накапливающем сумматоре обычно реализуется операция установки

. Накапливающий сумматор можно рассматривать как композицию регистра, используемого для хранения значения

и комбинационного сумматора

, вычисляющего сумму

. Структурная схема параллельного накапливающего сумматора изображена на рисунке 4,а, условное обозначение на операционных схемах – на рисунке 4,б.

Время такта суммирования в данном случае определяется задержкой комбинационного сумматора и временем приема значения суммы на регистр.

Пример 1. Реализовать параллельный накапливающий четырехразрядный сумматор, выполняющий микрооперации

на микросхемах К155ИМ3 – четырехразрядный параллельный комбинационный сумматор (рисунок 5) и К155ИР1 – четырехразрядный регистр (рисунок 7). Т(1:4) – внешний регистр.

Микросхема К155ИМ3 – быстродействующий комбинационный параллельный сумматор. Он принимает два четырехразрядных слова по входам данных А1-A4 и В1-В4, а по входу Р0 – сигнал входного переноса (переноса в младший разряд сумматора). Суммы разрядов входных слов появляются на выходах S1-S4. На выходе P выделяется сигнал переноса из старшего разряда сумматора. Старшим разрядом входных слов и суммы является четвертый разряд. Внутри сумматора имеется схема ускоренного переноса (СУП).

Вход и выход

могут быть использованы для наращивания разрядности сумматора.

Схема накапливающего сумматора на основе микросхем К155ИМ3 и К155ИР1 приведена на рисунке 6.

Логическая единица на входе микросхемы К155ИР1 обеспечивает постоянное нахождение регистра в режиме параллельной загрузки. Если в схему подан управляющий сигнал

, то в регистр загружается значение суммы, находящееся на выходах комбинационного сумматора. Если в схему подан управляющий сигнал

, то в регистр загружается ноль, т.к. в рассматриваемой схеме

. Если в схему не подается ни один из управляющих сигналов, то регистр хранит свое состояние, так как на вход управления параллельной загрузкой

не подается синхросигнал.

Последовательный накапливающий сумматор

Пример 2. Синтезировать последовательный n-разрядный накапливающий сумматор на базе ОКС (рассмотрен выше), сдвигающего регистра С(1:n) и триггера Р (для запоминания переноса).

Структурная схема последовательного сумматора приведена на рисунке 7. Первое слагаемое загружается в регистр С(1:n), например, с внешнего регистра T(1:n). Второе слагаемое подается на вход ОКС в последовательном коде.

Сложение осуществляется за n тактов. В очередном такте на ОКС складываются очередные цифры слагаемых и

и перенос

, полученный в предыдущем такте при сложении предыдущих младших цифр. Перенос

, полученный в текущем такте, запоминается на триггере для использования в следующем такте. По истечении n тактов сумма должна оказаться в регистре С. Для записывания в регистр очередного разряда суммы

и подачи следующей цифры первого слагаемого на ОКС используется микрооперация сдвига (при сдвиге в n-ном разряде регистра С оказывается следующая по старшинству цифра первого слагаемого, а освобождающийся старший разряд регистра С доопределяется значением очередной вычисленной цифры суммы). При сложении младших разрядов перенос должен быть равен нулю, поэтому необходимо предусмотреть микрооперацию сброса триггера Р. Если в триггере есть установочные входы, то сигнал

можно подавать на установочный R-вход триггера.

Процесс сложения при помощи последовательного сумматора является не микрооперацией, а микропрограммой (почему?).

Постройте самостоятельно функциональную схему четырехразрядного последовательного накапливающего сумматора на микросхемах серии К155.

0 коммент.:

Отправить комментарий