Как показывает практика, далеко не все микросхемы возможно использовать в радиолюбительском творчестве. Например, достаточно трудно применять такие варианты, как микросхемы для телевизионных приемников, формирователи сигналов разверток, корректоры цветовых переходов, декодеры цветности, синтезаторы частоты для мобильных телефонов и т. д. Поэтому в рамках данной книги рассматриваются микросхемы, которые могут быть использованы преимущественно в домашней аудиоаппаратуре, такой, как, например, усилители низкой частоты, усилители мощности, радиоприемники. Что-то подойдет для создания несложных и полезных устройств на основе микроконтроллера — охранные системы, системы сбора информации, электронные частотомеры, фазометры, генераторы. При необходимости получить информацию по другим типам микросхем можно непосредственно с сайта фирмы Philips (http://www.semiconductors.philips.com). Следует отметить, что оригинальная документация требует перевода с английского языка, а значит, необходимо приложить некоторые усилия тем, кто английский знает плохо или вообще не знает. Но при определенном навыке глубоких знаний не требуется и смысл большинства слов становится ясным без перевода.

Итак, перейдем к рассмотрению микросхем.

ЭСППЗУ с последовательным доступом

Микросхемы ЭСППЗУ (электрически стираемые постоянно программируемые запоминающие устройства) с последовательным доступом появились на рынке сравнительно недавно, но тем не менее они прочно вошли в арсенал разработчика. Международная аббревиатура микросхем — EEPROM (electrically erasable PROM). Истори-

чески первыми появились, впрочем, микросхемы с параллельным доступом, когда каждый бит байта мог быть считан или записан по отдельной линии, а значит, одновременно с другими битами. Адрес хранения байта задавался также параллельным способом. То есть, к примеру, память 8-разрядных данных на 256 ячеек должна содержать 8 линий данных и 8 линий адреса данных. Достоинством памяти с параллельным доступом является достаточно малое время доступа — данные транслируются одновременно по всем линиям. Управлять такой памятью тоже очень просто, достаточно выставить адрес, и данные будут считаны (записаны).

Гораздо сложнее работать с последовательной памятью. Во-пер- вых, необходимо последовательно, бит за битом, передать адрес ячейки памяти, затем точно так же передать (или считать) данные. Очевидно, скорость обмена с такой памятью в десятки раз меньше, чем с памятью параллельной. Что и сдерживало появление такого вида памяти. Массовый выпуск последовательных EEPROM начался после того, как в составе малогабаритной техники появились несложные микроконтроллеры. В основном такая техника не критична к высокой производительности вычислительных устройств, к ней относится бытовая и управляющая аппаратура. Еще одно важное обстоятельство, расширяющее возможности применения последовательных микросхем ЭСППЗУ, — их достаточно низкая стоимость.

Следует отметить, что для доступа к данным последовательной памяти используются разные интерфейсы: I2C, Microwire, SPI, CBUS. Некоторые сведения относительно номенклатуры микросхем можно почерпнуть в литературе [2]. Мы коснемся только тех, которые имеют интерфейс I2C. Обратите внимание: ЭСППЗУ с интерфейсом I2C, выпускаемые разными фирмами (SGS-Thomson microelectronics, Philips, Microchip) и имеющими одно наименование (например, 24С01), могут немного отличаться по расположению выводов, способу задания slave-адреса, особенности внутренней организации, принципам защиты от записи и др. При проектировании конкретных устройств рекомендуется ориентироваться не только на наименование ЭСППЗУ, но также и поинтересоваться фирмой-производителем, получить оригинальную техническую документацию.

Примеры применения EEPROM с последовательным доступом рассмотрим по документации [10, 11], относящейся к микросхемам

РСА8581 (128 х 8 битов) и PCF85xx (256... 1024 х 8 битов), производимых Philips, а также по мануалам [12, 13], описывающим микросхемы 24LC16B (2048 х 8 битов) и 24LC32A (4096 х 8 битов) производства фирмы Microchip.

РСА8581

Микросхема имеет два исполнения (без буквы «С» в окончании названия и с буквой), отличающихся по некоторым основным эксплуатационным характеристикам. Основные параметры микросхемы:

• питающее напряжение от 4,5 до 5,5 В (РСА8581) и от 2,5 до 6,0 В (РСА8581С);

• встроенный импульсный умножитель напряжения «зарядовый насос» для обеспечения режима записи (для программирования памяти нужно напряжение 12 В, в то время как микросхемы питаются пониженным напряжением);

• автоматическое стирание ранее записанной информации перед записью новой (режим automatic erase/write);

• ток потребления в дежурном режиме 10 мкА;

• задание slave-адреса с помощью трех внешних выводов (АО, А1.А2);

• автоматический инкремент адреса при обращении;

• минимально гарантированное число циклов записи — 10 000;

• минимально гарантируемое время сохранения записанной информации — 10 лет;

• бесконечно возможное число циклов чтения;

• рабочая температура окружающей среды от -25 до +85 °С;

• возможность использования на одной шине до 8 однотипных микросхем без дополнительных аппаратных средств переключения и расширения;

• максимальная частота SCL сигнала — 100 кГц (режим low-speed).

Микросхема выпускается в 8-выводном корпусе типа DIP8 или S08 (с планарными выводами). Расположение выводов приведено на рис. 3.1, а их назначение — в табл. 3.1.

Таблица 3.1. Назначение выводов РСА8581

| Символ | Вывод | Описание |

| АО | 1 | slave-адрес 0 |

| А1 | 2 | slave-aflpec 1 |

| А2 | 3 | slave-адрес 2 |

| f ^ | 4 | Общий вывод |

| SDA | 5 | Линия SDA вход/выход |

| SCL | 6 | Линия SCL вход |

| TEST | 7 | Тестовый вывод |

| vDD | 8 | Питание«+» |

Внутреннее устройство микросхемы показано на рис. 3.2.

Чтобы предохранить микросхему от перегрузок, например при воздействии статического электричества, разработаны и используются разные методы защиты. Наиболее эффективны, дешевы и носят массовый характер методы встраивания защитных диодов. Один из таких способов, примененный в данной микросхеме, показан на рис. 3.3.

Выводы конфигурации slave-адреса А0...А2 снабжены двумя последовательно включенными диодами. При превышении напряжения на выводах А0...А2 порога, заданного напряжением VDD, открывается верхний диод и «притягивает» вывод к потенциалу питания VDD. Если напряжение становится ниже Vss (потенциал общего провода), открывается нижний диод и «притягивает» вывод к потенциалу «земли» Vss. Обратите внимание: в данном случае выводы SDA и SCL имеют только защиту от отрицательного напряжения и не имеют за-

щиты от положительного (верхний диод отсутствует), поскольку микросхема может быть использована при напряжениях на шине, отличных от напряжения питания микросхемы.

Мы уже знаем, что обращение к микросхеме происходит посредством передачи по шине I2C slave-адреса, как показано на рис. 3.4. Адрес в данном случае состоит из 7 битов. Старшие 4 бита (1010) определяют принадлежность микросхемы к группе EEPROM, младшие 3 бита — АО, А1, А2 — задают уникальный идентификационный номер в группе однотипных микросхем. Если на шине присутствует несколько микросхем с одинаковыми старшими 4 битами slave-адреса, необходимо с помощью перемычек, подключаемых к напряжению питания или к общему проводу, задать на выводах А0...А2 потенциалы, назначить микросхемам уникальные идентификационные номера, например, как показано на рис. 3.5. Обращение к соответствующему элементу будет производиться программно, заданием битов А0...А2.

Разберемся теперь, как устроена матрица памяти микросхемы и каким образом осуществить запись (считывание) данных.

Рассмотрим сначала ситуацию, когда устройство master передает данные к slave-абоненту (режим записи WRITE). Формат сообщения представлен на рис. 3.7.

Вначале осуществляется передача slave-адреса и признака R/W (в данном случае этот бит установлен в «О»), Второй байт — адрес ячейки матрицы памяти, изображенной на рис. 3.6. Обратите внимание: старший бит этого байта, помеченный на рис. 3.7 знаком «х», не определяется или, другими словами, может быть установлен в «О» или в «1». Почему? Это станет понятным, когда мы представим, что с помощью 8 битов возможно задание 256 адресов, но в данной микросхеме присутствует только 128 ячеек (а значит, столько же и адресов). Старшие 128 адресов здесь просто не определены.

После передачи адреса ячейки осутествлясгся передача байта данных (DATA). Биты 7...О последовательно занимают ячейки памяти. После приема бита «О» данных осуществляется автоинкремент (увеличение на единицу) адреса памяти. Естественно, завершение передачи должно сопровождаться появлением условия Stop.

Чтение из памяти осуществляется по протоколу, показанному на рис. 3.8.

Вначале необходимо передать slave-адрес с признаком R/W — «О», затем адрес ячейки. После получения master-абонентом сигнала АСК, свидетельствующего о нормальном приеме адреса ячейки памяти, master-абонент должен выставить повторное условие Start и передать slave-устройству slave-адрес с признаком R/VV -— «1», получить АСК от slave-устройства и начать считывание данных, выставляя после каждого полученного байта сигнал АСК. После получения последнего байта master-абонент не выставляет сигнала АСК, а выполняет условие Stop. Заметим, что в данном случае также справедлив автоинкремент адреса ячейки.

Master-абонент может начать непосредственное чтение со slave-устройства, но в этом случае он должен учитывать, что чтение будет производиться не с нулевого адреса, а с увеличенного на единицу адреса, операция с которым была последней в предыдущем цикле (рис. 3.9).

PCF85xx

Эта серия микросхем EEPROM имеет увеличенный объем памяти по сравнению с предыдущей микросборкой. Емкость микросхем серии указана в табл. 3.2.

Таблица 3.2

| Микросхема | Емкость | Организация j | |

| PCF8582 | 2 кбита | 256 х £ | битов |j |

| PCF8594 | 4 кбита | 512 х | битов J |

| PCF8598 | 8 кбитов | 1024 х | 8 битов if |

совместимы с чипами PCF8570, PCF8571, PCF8572 и PCF8581 по расположению выводов. Внутренее устройство микросхем PCF8582, PCF8594 и PCF8598 приведено на рис. 3.10.

Расположение выводов указанных микросхем приведено на рис. 3.11, назначение выводов — в табл. 3.3—3.5.

Таблица 3.3. Назначение выводов PCF8582

| Символ | Вывод | Описание |

| АО | 1 | Slave-адрес 0 |

| А1 | 2 | Slave-адрес 1 |

| А2 | 3 | Slave-адрес 2 |

| Vss | 4 | Общий вывод |

| SDA | 5 | Линия SDA вхо/^выход |

| SCL | 6 | Линия SCL вход |

| РТС | 7 | Контроль времени программирования |

| Vdd | со | Вывод питания«+» |

Таблица 3.4. Назначение выводов PCF8594

| Символ | Вывод | Описание |

| WP | 1 | Защита записи |

| А1 | 2 | Slave-адрес 1 |

| А2 | 3 | Slave-адрес 2 |

| Vss | 4 | Общий вывод |

| SDA | 5 | Линия SDA вхо^выход |

Таблица 3.5. Назначение выводов PCF8598

| Символ | Вывод | Описание |

| WP | 1 | Защита записи |

| - | 2 | Не используется |

| А2 | 3 | Slave-aflpec 2 |

| Vss | 4 | Общий вывод |

| SDA | 5 | Линия SDA вход/выход |

| SCL | 6 | Линия SCL вход |

| РТС | 7 | Контроль времени программирования |

| Vdd | 8 | Вывод питания«+» |

Протокол программирования памяти микросхем аналогичен приведенному ранее, но имеет некоторые особенности. Одна из особенностей связана с тем, что адрес ячейки памяти пе может содержать число, превышающее 255. Но приведенные тины микросхем содержат 512 и 1024 ячейки. Что это означает? Все очень просто: в slave-адресе биты Л0...А2 уже не все программируются внешними перемычками. Часть из них выбирается программно, при задании shve-адреса. Мы словно объединяем в одном корпусе несколько микросхем PCF8582. Структура памяти, состоящая из блоков по 256 байтов, называется страничной организацией. К слову, максимальное число страниц в одной микросхеме 8.

Интересной возможностью, реализованной в описываемых микросхемах, является возможность защиты от повторной записи. Если вывод WP имеет низкий уровень, работа с EEPROM не имеет ограничений. Если WP устанавливается в состояние «1», верхняя половина памяти EEPROM защищается от записи. В таком случае сигнал АСК пе будет генерироваться при адресации к верхней половине (256 байтов) PCF9594 и PCF8598 (512 байтов).

При записи данных в память EEPROM должны быть выдержаны определенные временные соотношения (циклы erase/write). Длительность этих циклов формируется внутри микросхемы и в большинстве случаев не требует коррекции. Если коррекции не требуется, вывод РТС может быть подключен к VDn или оставлен не подключенным. Типичное значение Бремени tr vv г= 7 мс, оно может быть задано внешне в пределах 4... 10 мс.

Как уже ранее было сказано, микросхемы EEPROM с последовательным доступом по шине ГС выпускает не только фирма Philips, но и другие не менее известные фирмы. Для сравнения приведем описания микросхем 24LC16B и 24LC32A, производимых Microchip.

24LC16B

Емкость микросхемы —- 16 кбитов, организованных в 8 блоков по 256 битов. Основные характеристики:

• возможность питания пониженным напряжением (до 2,5 В):

• наличие входных формирователей (триггеров Шмитта) для обеспечения помехоустойчивости;

• ток потребления в активном режиме 1 мА;

• потребление в режиме ожидания — 10 мкА при питании 5,5 В и 5 мкА при питании 3,0 В:

• организация 8 х 256 х 8 би тов;

• зашита входов от потенциального пробоя 4 кВ:

• возможность работы в режиме fast-speed;

• автоматическое выполнение цикла E/W;

• внутренний буфер данных размером 16 байтов;

• типичный цикл записи страницы данных ■—- 2 мс;

• аппаратная защита от перезаписи;

• гарантированное число циклов E/W — 1 ООО ООО;

• сохранность записанных данных — не менее 200 (!) лет;

• коммерческое (0...+70 °С) и индустриальное (-40...+85 °С) исполнения;

• корпуса DIP и SOIC.

Расположение выводов показано на рис. 3.12.

Запись в память и считывание из нее осуществляется по принципам, описанным выше, поэтому мы не будем повторяться.

Очень важный момент, на который обращают внимание разработчики микросхемы, связан с повторным обращением к памяти вслед за завершением предыдущего цикла. Другими словами, после установки условия Stop внутри микросхемы начинается процесс записи в матрицу памяти и, пока он не закончится, совершать повторные операции не представляется возможным.

Особенно это будет заметно в режиме fast-speed, поскольку в нем используются ускоренные шинные циклы. Сообщить об окончании внутренних операций микросхема может только при помощи установки сигнала АСК в состояние «О». Для сокращения времени опознавания разработчики рекомендуют производить эту процедуру с помощью так называемого поллинга (acknowledge polling flow), то есть постоянного опроса состояния готовности. Процедура поллинга приведена на рис. 3.13.

Как следует из рис. 3.13, master-абонент вслед за передачей условия Stop выставляет условие Start, передает slave-адрес и проверяет сигнал АСК. Если АСК = 1 (занято), передается повторно условие Start, slave-адрес, осуществляется проверка АСК. Если АСК = 0 (свободно), master-абонент переходит к следующей операции.

Память можно защитить от записи, подключив вывод WP к напряжению VDD. Обратите внимание: таким образом защищается полный объем памяти (OOOh—7FFh), а не ее часть (верхняя или нижняя). Защищенная память представляет собой тип ROM с последовательным доступом (read-only, только чтение).

Внутреннее устройство микросхемы, приводимое в технической документации, вы можете увидеть на рис. 3.14.

На рис. 3.14:

• — порт ввода/вывода;

• — контроллер памяти;

• — декодер «X»;

• — генератор высокого напряжения;

• — матрица памяти;

• — селектор страниц;

• — декодер «У»;

• — схема контроля R/W.

24LC32A

Пожалуй, это наиболее интересная микросхема, позволяющая хранить 32 кбита информации. «Как же так, — спросите вы, — неужели возможно без специальных средств обеспечить хранение и обмен информации, превышающей 16 кбитов?» Оказывается, можно. Причем никаких дополнительных микросхем расширения не потребуется — все необходимые средства уже есть в составе описываемой EEPROM.

Мы не будем останавливаться на параметрах микросхемы, так как они в основном совпадают с теми, что были приведены для 24LC16B. Расположение выводов показано на рис. 3.15, внутреннее устройство — на рис. 3.16. Назначение блоков совпадает с рис. 3.14.

Вы уже обратили внимание на наличие выводов АО...A3, позволяющих селектировать slave-адрес и «повесить» на шину I2C до 8 таких микросхем? Не будет ли здесь путаницы, шинного конфликта? В самом деле, классический вариант может адресовать только 256

ячеек, переключая страницы посредством задания определенных уровней сигнала на выводах АО...A3 или программируя их в slave-адресе. Дело в том, что данная микросхема имеет два адресных бита, следующих за slave-адресом, как показано на рис. 3.17.

Матрица памяти разделена здесь также на блоки по 256 байтов, но селектируются они уже не посредством задания битов А0...А2 в slave-адресе, а битами А8...А11 в адресном бите 1.

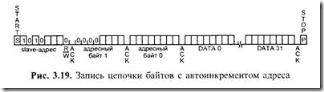

Операции записи байга, записи цепочки байтов с автоинкрементом адреса, чтения байта и чтения байта с автоинкрементом приведены на рис. 3.18...3.21. Дополнительных пояснений рисунки не требуют.

Добавлю, что в данной микросхеме предусмотрен вывод WP, позволяющий выполнить защиту от записи. Здесь также может быть использована процедура программного поллинга для обеспечения быстрого повторного доступа.

К5004РС2,КР5004РР4

Отечественная промышленность хоть и с большим опозданием, но все же собирается выпустить на рынок микросхемы памяти с последовательным доступом и интерфейсом, один к одному соответствующим I2C [17, 18]. И хотя на момент написания этой книги доку- ментация пока еще имеет гриф «предварительно», возможно, что ко дню выхода этой книги из печати микросхемы К5004РС2 и КР5004РР4 производства ОАО «Ангстрем», г. Зеленоград уже появятся в продаже.

Что же это за микросхемы? Просматривая документацию, вы не найдете там упоминания об Т2С, но, сравнив принципы доступа с фирменными, приведенными чуть выше, можно убедиться в полной совместимости с этой шиной. Мало того, интерфейсные линии имеют обозначения SCL и SDA, как у лицензированных микросхем I2C.

Микросхема К5004РС2 (АДБК.431210.792 ТУ) совместима с режимами low-speed и fast-speed. Она организована страницами по 8 байтов. Количество страниц — 32. Запись осуществляется блоками размером от 1 до 8 байтов в одной странице, при одном цикле записи. Питается микросхема напряжением 2,7...5,5 В, имеет аппаратную защиту от записи.

Микросхема КР5004РР4 (АДБК.431210ю737 ТУ) также совместима с режимами low-speed и fast-speed, организована страницами по 8 байтов. Количество страниц — 64, питание от 4,5 до 5,5 В. Обе микросхемы будут выпускаться в двух корпусах — DIP8 и SOIC.

В чем же может заключаться преимущество данных микросхем перед импортными? Пожалуй, только в цене.

Литература:

Б. Ю. Семенов, «ШИНА 12С В РАДИОТЕХНИЧЕСКИХ КОНСТРУКЦИЯХ» ,Москва СОЛОН-Р 2002

![clip_image002[4] clip_image002[4]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEjzvvTUW_Ws8TttvxcmTpE6gozf_BpPFdpgFwPmhIII_BcJSthmBAcqgmaSH9HusssmaliZRrxZrrOtZB88PM62gdtdzk9jDGwyk9Sy-w2KTUdl67gBdyAB3oxTBCS1aNHbWxuvlJKiLAs/?imgmax=800)

![clip_image004[4] clip_image004[4]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEhjkedgh22pexPMvqUZaJsStFMJsIwazRPkqyjJ7eRvdfMnJgBFU0Z2W6TGHEuI6xDYqHUIzthD8ZbNILIh-xXzmVkcmyI8tOZG2v_HqeraZl9KNVl6W6fwbVzGQgdKV-BMlGGr9BpRs84/?imgmax=800)

![clip_image006[4] clip_image006[4]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEiIYR8YWczLYpBpqrO5Py9W0h4k9aRgvIn0Wg2VjZS2Noo7l6t2jp0Vrrtb-_SZIwcy3W1z1EOUv7-VlbfB2UZoueYjOieXv67eFuZxfKFFt47d3S4UUHs1EhcrojDFB_uu_G8BNI0OQ4s/?imgmax=800)

![clip_image008[4] clip_image008[4]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEgdONvSG3leSpDRBR8flZhXwiazK9PW9rZr0zbPLZ4idmkMteDg08prGcCkq5O0B8ckv-jsShX5_EqzE9bwuvyVQqal_9q5IDWEjDhUEgX5ZzoMaTDT7h0EyQOJiEVP-QnDRkUkmCHufPU/?imgmax=800)

![clip_image010[4] clip_image010[4]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEhReWkbY1tALcgGf_75u919d5Wq1OGdXnvhYmyhmjWJDJ386POcvGYaDUM0EJx149nbakwdK8VaSoVofrC6VZ0ERWB3dG5vUf1d-Gf13IrB3ImgzJ1Z4l19ZNtHSejtZVoyyZHMExCOP8E/?imgmax=800)

![clip_image012[4] clip_image012[4]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEikuY6hQsigfmKT9epKwYLFViKrhWwMMnzOp0o0Q3jS849dWB7eMLVzAthkxh7evkp6FrQ_4lXpvkE5WSznLRoM2jD1qOshlRcwO1n6ELMZltLqhzJNSYKpqX9EB2AkFq9KdjFFB7lo-Qs/?imgmax=800)

![clip_image014[4] clip_image014[4]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEjjm0U9I4MPofJyE9yWSVUdWSkEhOhg2zW3CrOwklOZO87dQ8FixY0p5cUtL1ePMf0lAEBPGcof_YbMJ-pwX-PsNgBJDThnIGwZ77QPgmBskJQeKiveXZzXd_aQWwQSYINfaCBkAECPT50/?imgmax=800)

![clip_image016[4] clip_image016[4]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEiG4ufkAptzUZzQeUl9YDuiqQEZqM3RVG7S3ef7eW6Ns6jSPlpqNHJH4R-Oe06sW-xvJPBlGrusu2W3JdWT17657FhmBKDxly49zKrGJ4GvY_lc0Oz5t7TNDx6MJ5-QW_U0HskOytRJP0I/?imgmax=800)

![clip_image018[4] clip_image018[4]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEi6YgKr3Y6HBIu6EuIaNgzNEVgPVaEwa1YMrxUjEDTrAHv53UBDUsBcYMn85sfXy4h47UR3nMIPpz2MutnZ9fCuhPZ7fGiEu_JTaChYp4db7V5-g3864Lwr3SRbGbpqD2-DY7gB-OyKKN0/?imgmax=800)

0 коммент.:

Отправить комментарий