TDA1551Q

В оригинальной документации [19] эта микросхема классифицируется как BTL car radio amplifier with diagnostic facility, или в переводе на русский язык — автомобильный мостовой усилитель мощности (УНЧ) со встроенными средствами диагностики состояния.

Естественно, данную микросхему можно применять не только в автомобильной технике, но также и для создания высококачественного бытового стереоусилителя. Вообще похожие микросхемы, которые не снабжены интерфейсом I2C для диагностики состояния, широко распространены на отечественном рынке радиодеталей. К примеру, это TDA1519A, TDA1552Q, TDA1553Q, TDA1570Q, TDA8920 и многие другие. Однако микросхема TDA1551Q — значительный шаг вперед по сравнению с указанными микросборками в плане сервисных возможностей. Итак, что сказано в предуведомлении:

• наличие минимального количества внешних навесных элементов;

• возможность использования в четырехканальном и мостовом двухканальном вариантах;

• управление и контроль посредством шины I2C;

• наличие детектора динамических искажений;

• тепловая защита;

• наличие детектора пониженного напряжения питания;

• высокая выходная мощность;

• наличие режимов MUTE (блокировка звука) и SLEEP («засыпание»), задаваемых по шине ГС;

• дополнительное подавление пульсаций питающего напряжения;

• наличие схемы защиты нагрузки;

• наличие схемы защиты по постоянному и переменному току от замыканий выходных контактов на общий провод и на шину питания;

• низкое тепловое сопротивление корпуса;

• наличие равноправных входов (инвертирующего и не инвертирующего).

Микросхема представляет собой усилитель низкой частоты класса В, размещенный в удобном корпусе SOT243R (рис. 3.33). Расположение выводов показано на рис. 3.34, а их назначение — в табл. 3.13.

Таблица 3.13. Назначение выводов микросхемы

| I Символ | Вывод | Описание |

| -INV1 | 1 | Неинвертирующий вход 1 |

| INV1 | 2 | Инвертирующий вход 1 |

| GND | 3 | Сигнальная «земля» |

| Vprr | 4 | Вывод подключения конденсатора фильтра |

| 5 | Вывод питания 1 | |

| ______ 0UT1 | 6 | Выход 1 |

| GND1 | 7 | «Земля» шины питания 1 |

| 0UT2 | со | Выход 2 |

| SB | 9 | Вывод «дежурный режим» |

| 01ЯЗ | 10 | Выход 3 |

| GND2 | 11 | «Земля» шины питания 2 |

| OUT4 | 12 | Выход 4 |

| V | 13 | Вывод питания 2 |

| INV2 | 14 | Инвертирующий вход 2 |

| -INV2 | 15 | Неинвертирующий вход 2 |

| j SCL SDA | 16 | Линия SCL шины I2C |

| 17 | Линия SDA шины I2C |

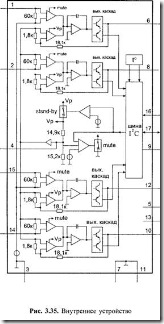

Внутреннее устройство микросхемы TDA1551Q показано на рис. 3.35. Основные параметры микросхемы, необходимые для проектирования, приведены в табл. 3.14.

Таблица 3.14

Окончание таблицы 3,14

| Параметр технических условий | Символ | Мин. | Норма | Макс. | Ед. изм. | |

| Коэффициент усиления | Gv | 19 | ' 20 | 21 | ДБ i |

| Входной импеданс | 50 | 60 | 75 | кОм | |

| Разделение каналов | a | 40 | дБ | ||

| Небаланс каналов | - | - i. 1 | ДБ | ||

| Параметры интерфейса I2C | |||||

| Входной сигнал высокого уровня | 3 | - | 5,5 | в ; | |

| Входной сигнал низкого уровня | Ч, | -0,3 | - | 1,5 | в |

| Выходной сигнал низкого уровня | - | - | 0,4 | 00 ! го | |

| Срабатывание схемы внутреннего сброса: старт окончание | v | 3 - | _ | 5 | |

| Standby (вывод 9) I_ _ _ . ... . | 4iigh Vlov | 3 | - | p 2 | в |

Как видно из рис. 3.35, микросхема состоит из четырех идентичных усилителей с дифференциальными входными каскадами, один из которых является инвертирующим, а второй — неинвертирующим. Как известно, для обеспечения нормальной работы любого элемента необходимо рассчитать его тепловой режим, принять меры к рассеянию излишней тепловой мощности. Например, в книге [3] приводится вариант такого теплового расчета. Собственно, нужно проверить необходимость проектирования теплоотводящего радиатора и рассчитать его габариты, выбрать конструктивное исполнение. Фирменная документация имеет все необходимые данные для расчета. Для удобства разработчика приводятся размеры теплоогводящей поверхности (рис. 3.36, a) и внутреннее распределение тепловых сопротивлений между теплоотводящей поверхностью и выводами микросхем (рис. 3.36, б).

Теперь разберемся, как управлять режимами микросхемы и как получать информацию о ее внутреннем состоянии. Мы уже неоднократно говорили, что «общение» с микросхемой происходит программно. Обратите внимание на рис. 3.37: по шине I2C передается фиксированный slave-a;ipec микросхемы, а также единственное слово данных (DATA). Условие «R7W», как обычно, отражает режим записи/чтения.

Конфигурирование происходит при передаче бита «R/W», установленного в «О» (режим записи данных). Возможные состояния байта DATA приведены в табл. 3.15, но вообще можно сказать, что бит DO «отвечает» за переключение микросхемы из режима SLEEP в режим ON и обратно, бит D1 переключает в режим MUTE.

Таблица 3.15

| Установка битов D7...D0 | Состояние | |||||||

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | SLEEP |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | MUTE |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | Тест' |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | ON2 |

Примечания.

• Состояние используется только для тестирования. Шина I2C работает в режиме ON, в го время как усилитель переведен в состояние standby.

• Включение в состояние ON после подачи питания недопустимо, так как это может вывести микросхему из строя. Необходимо вначале переключить микросхему из состояния SLEEP в состояние MUTE и только затем, за время не менее 150 мс, перевести в состояние ON.

Возможные варианты переключения микросхемы из одного состояния в другое показаны на рис. 3.38.

Чтобы получить информацию о внутреннем состоянии микросхемы, провести ее диагностику, достаточно осуществить чтение по формату, изображенному на рис. 3.37, установив бит «R/W» в состояние «1». В таком случае биты D7...D0 несут следующую информацию:

• D7 устанавливается в состояние «О» после операции чтения на шине I2C;

• D7 устанавливается в состояние «1» после начального сброса при включении питания;

• D6 не используется;

• D5 устанавливается в состояние «О», если температура кристалла менее +150 °С;

• D5 устанавливается в состояние «1», если температура кристалла превышает +150 °С;

• D4 устанавливается в состояние «0», если микросхема не входит в режим ограничения сигнала (общие гармонические искажения THD менее 3,5%);

• D4 устанавливается в состояние «1», если микросхема находится в режиме ограничения сигнала (общие гармонические искажения THD более 3,5%);

• биты D3...D0 определяются согласно табл. 3.16.

Таблица 3.16

| D3 | D2 | D1 | DO | Функция |

| 0 | 0 | 0 | 0 | Все выходные каскады в норме |

| X | X | X | 1 | Неисправность на выводе 6 |

| X | X | 1 | X | Неисправность на выводе 8 |

| X | 1 | X | X | Неисправность на выводе 10 |

| 1 | X | X | X | Неисправность на выводе 12 |

Примечание: если неисправность случится в нескольких каскадах, соответственно одновременно будут установлены в состояние «1» биты, информирующие о неисправности в конкретном канале.

На рис. 3.39 и рис. 3.40 показаны типовые варианты включения микросхемы.

TDA8424

В документации [20] эта микросхема называется Hi-Fi stereo audio processor или, говоря по-русски, высококачественный стереофонический аудиопроцессор. Необходимо сразу оговориться, что фирма Philips выпускает несколько разновидностей аудиопро- цессоров, отличающихся друг от друга не слишком значительно. Например, при написании этой книги автор ознакомился с документацией на микросхемы TDA8421, TDA8425, TDA8426, TDA9860, ТЕА6300, ТЕА6324Т, ТЕА6330Т [22—28]. Было выяснено, что в рамках данной книги имеет смысл подробно описать только принци-

пы работы с какой-нибудь одной микросхемой этого вида. С остальными читатель при необходимости разберется самостоятельно. Оригинальную документацию можно получить с официального сервера Philips (http://www.semiconductors.philips.com).

Несколько слов о том, зачем нужен аудиопроцессор и где его можно применить. Вспомним, что в составе любого стереокомплекса или телевизора обязательно имеются органы регулировки громкости, стереобаланса, тембра. В классическом варианте на переднюю панель всегда выводились отдельные ручки регулировок «громкость», «тембр НЧ», «тембр ВЧ», «стереобаланс». Современная аппаратура таких органов регулировки уже не имеет, хотя они все равно присутствуют в ее составе. Все дело в том, что теперь эти органы «прячут» в электронной схеме прибора, а о состоянии того или иного регулятора свидетельствует соответствующая надпись на жидкокристаллическом (или электролюминесцентном) индикаторе, «бегущая полоска» на экране телевизора. Управление осуществляется только с помощью кнопок, данные поступают в управляющую микросхему в цифровом виде.

Итак, рассмотрим микросхему TDA8424, предназначенную для электронной регулировки тембра, громкости, стереобаланса. Микросхема в своем составе имеет:

• селектор режимов;

• переключатель режимов «пространственное (spatial) стерео» (расширенная стереобаза) «стерео», «принудительное моно»;

• схемы управления громкостью и стереобалансом;

• схемы управления тембровой окраской по высоким (ВЧ) и низким (НЧ) частотам;

• аппаратный сброс при включении питания.

Селектор режимов используется для задания режимов «стерео», «sound А», «sound В» для трансляции звука только из правого или только из левого канала.

Управление громкостью и стереобалансом совмещенное. Регулятор громкости состоит из двух каскадов, предназначенных для прохождения сигналов левого и правого каналов. Коэффициент передачи каждого каскада может быть отрегулирован в пределах от 6 до -64 дБ с шагом 2 дБ. Дополнительно можно получить затухание

-80 дБ. Оба канала управляются независимо друг от друга, поэтому возможна регулировка с гереобаланса.

Режимы «spatial стерео», «стерео» и «принудительное моно» могут быть использованы в разных ситуациях. Режим «стерео» используется в случае прохождения обычного стереосигнала. При получении соответствующей команды, свидетельствующей об отсутствии стереосигнала, микросхему можно перевести в режим «spatial стерео» (расширенная стереобаза) или «принудительное моно».

Регулировка тембра по низким частотам (НЧ) осуществляется в пределах от 15 до -12 дБ с шагом 3 дБ. .

Регулировка тембра по высоким частотам (ВЧ) осуществляется в пределах от 12 до -12 дБ с шагом 3 дБ.

Расположение выводов показано на рис. 3.41, назначение выводов — в табл. 3.17, внутреннее устройство микросхемы — на рис. 3.42.

Таблица 3.17. Назначение выводов микросхемы

| Символ | Вывод | Описание |

| INL | 1 | Вход левого канала |

| Чар | 2 | Развязывающий конденсатор |

| INR | 3 | Вход правого канала |

| Vcc | 4 | Питание«+» |

| AGND | 5 | Аналоговая «земля» |

| BASS R | 6 | Управление НЧ правого канала |

Окончание таблицы 3.17

| Символ | Вывод | Описание | |

| BASS R | 7 | Управление НЧ правого канала | |

| TREBLE R | 8 | Управление ВЧ правого канала | : |

| OUT R | 9 | Выход правого канала | |

| DGND | 10 | Цифровая «земля» | |

| SDA | 11 | Линия SDA шины I2C | |

| SCL | 12 | Линия SCLiuHHbi I2C | |

| ! OUT L | 13 | Выход левого канала | ! |

| TREBLEL | 14 | Управление ВЧ левого канала | |

| BASS L | 15 | Управление НЧ левого канала | |

| BASS L | 16 | Управление НЧ левого канала | |

| - | 17 | Не используется | |

| 18 | Не используется | ||

| 19 | Не используется | ||

| 20 | Не используется |

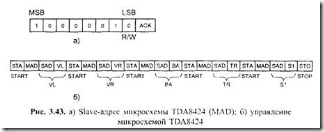

Теперь поговорим о том. как управлять данной микросхемой. Slave-адрес фиксирован жестко и показан на рис. 3.43, а. В дальнейшем описании, касающемся данной микросхемы, на всех рисунках этот адрес будет обозначен как MAD.

После slave-адреса следует серия субадресов, которые задают местоположение ячеек, регулирующих:

• громкость левого канала;

• громкость правого канала;

• тембр НЧ в обоих каналах;

• тембр ВЧ в обоих каналах.

В табл. 3.18 приведено кодирование байта с условным наимено- занием SAD, следующего после байта MAD. Не забывайте также о 1аличии сигналов АСК по окончании передачи каждого байта.

Таблица 3.18

| Функция | Адрес SAD | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| Громкость, левый канал | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Громкость, правый канал | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| НЧ-тембр | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| ВЧ-тембр | 0 | 0 | 0 | 0 | 0 ! 0 i | 1 | 1 i | |

| Функция переключения | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

В табл. 3.19 приводятся способы кодирования байта, следующего после байта SAD. Наименование этого байта меняется в зависимости от выполняемой функции (VL, VR, В A, TR, S1) и будет описано ниже.

Таблица 3.19

| Функция | 7 | 6 | СП | 4 | 3 | 2 | 1 | 0 |

| Громк., лев. кан. (VL) | 1 | 1 | V05 | V04 | V03 | V02 | V01 | V00 |

| Громк., прав. кан. (VR) | 1 | 1 | V15 | V14 | V13 | V12 | V11 | VI0 |

| НЧ-тембр (ВА) | 1 | 1 | 1 | 1 | ВАЗ | ВА2 | ВА1 | ВАО |

| ВЧ-тембр (TR) | 1 | 1 | 1 | 1 | TR3 | TR2 | TR1 | TR0 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| Функц. переключ. (S1) | 1 | 1 | ми | ЕЯ. | STL | ML1 | ML0 | 1 |

Таблица 3.21

| Режим | STL | EFL |

| Spatial стерео | 1 | 1 |

| Стерео | 1 | 0 |

| Запрещенное состояние | 0 | 1 |

| Принудительное моно | 0 | 0 |

Таблица 3.20

| Функция | ML1 | ML0 |

| Стерео | 1 | 1 |

| Канал А | 0 | 1 |

| Канал В | 1 | 0 |

Как вы уже успели заметить, в табл. 3.19 многие позиции четко не определены и заданы буквенно. Из табл. 3.19 также видно, что между позициями «ВЧ-тембр (TR)» и «Функц. переключ. (S1)» оставлено четыре незаполненных строки таблицы. Это связано с наличием в микросхеме режима автоинкремента. Если вы обратите внимание на табл. 3.18, то увидите разрыв кодов адресов SAD между упомянутыми позициями. Чтобы лишний раз не задавать адрес SAD (например, при первоначальном включении микросхемы), достаточно передать нулевой адрес SAD, затем значения позиций «Громк., лев. кан. (VL)», «Громк., прав. кан. (VR)», «НЧ-тембр (ВА)», «ВЧ-тембр (TR)», затем — 4 незначащих позиции, «забитых» единицами, и завершить позицией «Функц. переключ. (S1)». При этом после получения каждой позиции внутренний счетчик SAD будет автоматически инкременти- роваться. Дополнительная информация задается из табл. 3.20—3.25.

Таблица 3.22

| Режим MUTE (немой) | ми |

| Автоматически устанавливается после сброса | 1 |

| Неактивный | 0 |

Примечание: индекс «х» означает, что необходимо определить (согласно табл. 3.19) назначение данного бита. Например, обозначение V05 относится к байту VL, а обозначение VI5 — к байту VR.

Табл. 3.23—3.25 относятся к заданию уровня громкости, НЧ- и ВЧ-тембра.

Таблица 3.23. Регулировка уровня громкости

| Уровень громкости, дБ | V,5 | Vx4 | Vx3 | V*2 | V„1 | V*0 |

| со | 1 | 1 | 1 | 1 | 1 | 1 |

| 4 | 1 | 1 | 1 | 1 | 1 | 0 |

| 2 | 1 | 1 | 1 | 1 | 0 | 1 1 |

| 0 | 1 | 1 | 1 | 1 | 0 | 0 |

| -2 | 1 | 1 | 1 | 0 | 1 | 1 |

| -4 | 1 | 1 | 1 | 0 | 1 | 0 |

| -6 | 1 | 1 | 1 | 0 | 0 | 1 |

| -8 | 1 | 1 | 1 | 0 | 0 | 0 |

| -10 | 1 | 1 | 0 | 1 | 1 | 1 |

| -20 | 1 | 1 | 0 | 0 | 1 | 0 |

| -30 | 1 | 0 | 1 | 1 | 0 | 1 |

| -40 | 1 | 0 | 1 | 0 | 0 | 0 |

| -50 | 1 | 0 | 0 | 0 | 1 | 1 |

| -60 | 0 | 1 | 1 | 1 | 1 | 0 |

| -62 | 0 | 1 | 1 | 1 | 0 | 1 |

| -64 | 0 | 1 | 1 | 1 | 0 | 0 |

| -80 | 0 | 1 | 1 | 0 | 1 | 1 |

Таблица 3.24. Регулировка тембра НЧ

| Уровень, дБ | ВАЗ | ВА2 | ВА1 | ВАО |

| 15 | 1 | 0 | 1 | 1 |

| 12 | 1 | 0 | 1 | 0 |

| 9 | 1 | 0 | 0 | 1 |

| 6 | 1 | 0 | 0 | 0 |

| 3 | 0 | 1 | 1 | 1 |

| 0 | 0 | 1 | 1 | 0 |

| -3 | 0 | 1 | 0 | 1 |

| -6 | 0 | 1 | 0 | 0 |

| -9 | 0 | 0 | 1 | 1 |

| -12 | 0 | 0 | 1 | 0 |

Таблица 3.25. Регулировка тембра ВЧ

| Уровень, дБ | TR3 | TR2 | TR1 | TR0 |

| 12 | 1 | 0 | 1 | . 0 |

| 9 | 1 | 0 | 0 | 1 |

| 6 | 1 | 0 | 0 | 0 |

| 3 | 0 | 1 | 1 | 1 |

| 0 | 0 | 1 | 1 | 0 |

| -3 | 0 | 1 | 0 | 1 |

| -6 | 0 | 1 | 0 | 0 |

| -9 | 0 | 0 | 1 | 1 |

| -12 | 0 | 0 | 1 | 0 |

Кодирование микросхемы осуществляется согласно рис. 3.43, б.

При этом последовательность задания уровней VL, VR, ВА, TR и S1 не имеет значения. Разработчики рекомендуют устанавливать S1 в самом конце кодирования, когда остальные установки уже произведены. После включения питания необходимо провести полное конфигурирование, а в дальнейшем можно менять какой-то один параметр или их группу, например, только VL и VR. Тогда в информационном пакете будут отсутствовать байты ВА, TR, S1.

Возможно использование режима автоинкремента субадреса, как показано на рис. 3.44. В этом случае в байте SAD задается субадрес VL, а затем производится передача согласно рис. 3.44. Режим автоинкремента субадреса удобно использовать после первоначального старта (сброса схемы после включения питания). Символ «х» в данном случае означает, что необходимо повторить передачу неинформативных байтов согласно табл. 3.19.

Основные характеристики микросхемы, важные для проектирования, приведены в табл. 3.26.

Таблица 3.26

| Параметр технических условий | Символ | Мин. | Норма | Макс. | Ед. изм. |

| Напряжение питания | Чс | 10,8 | 12,0 | 13,2 | В |

| Ток потребления | 'сс | - | 26 | 35 | мА |

| Внутреннее опорное напряжение | Че, | 5,4 | 0,5VCC | 6,6 | В |

| Рабочая температура | ^amb | 0 | - | +70 | 'С |

| Температура хранения | Tstg | -25 | - | +150 | "С |

| Разделение каналов (на частоте 10 кГц) | acs | - | 80 | - | ДБ |

| Входной уровень сигнала (выводы 1 и 3) | Ч | 2 | - | - | В |

| Входное сопротивление | Ri | 20 | 30 | 40 | кОм |

| Полоса пропускания (по уровню 0,5 дБ) | В | 20 | - | 20000 | Гц |

| Выходное напряжение (выводы 9 и 13) | Ч, | 0,6 | - | - | В |

| Выходной импеданс | Zo | - | - | 100 | Ом |

| Уровень шума: усиление 6 дБ усиление 0 дБ ослабление < -20 дБ | S + N N | - | 78 86 68 | - | ДБ |

| Общие гармонические искажения: [6 дБ...-40 дБ] V, = 0,3 В [0 дБ...-40 дБ] V; = 0,6 В [12 дБ...-40 дБ] V, = 2,0 В | THD | - | 0,05 0,07 0,1 | 0,4 | % |

На рис. 3.45—3.47 приведены некоторые графические данные, которые наглядно свидетельствуют о высоком качестве микросхемы.

Микросхема выпускается в корпусе DIP20 (SOT 146-1) и предназначена для установки в печатную плату с шагом 2,54 мм. Типовая схема включения приведена на рис. 3.48.

ТЕА6360

В оригинальной документации [21] эта микросхема называется 5-band stereo equalizer circuit. Что такое эквалайзер, знают многие. А кто не знает, тому достаточно вспомнить несколько импортных магнитол и музыкальных центров, в которых это устройство имеется. Эквалайзер всего лишь расширенный вариант регулятора тембра, который позволяет более точно влиять на тоновую окраску звучания, выбирать ее по своим индивидуальным предпочтениям. Сложные профессиональные студийные эквалайзеры имеют не один десяток

частотных «линеек», позволяющих индивидуально подобрать звучание в каждом канале (каналов может быть четыре и более). Бытовая аппаратура, конечно, намного проще, и часто ее возможности ограничиваются всего пятью «линейками», представленными на передней панели прибора пятью движковыми переменными резисторами.

Микросхема ТЕА6360 позволяет отказаться от ненадежных резисторов, исключить характерный «скрип» при их старении, упростить интерфейс пользователя. Кроме того, в память прибора возможно занести несколько выбранных настроек, оперативно переключать их, а не заниматься подбором «с нуля». Внутреннее устройство микросхемы if ее типовое включение показаны на рис. 3.49, устройство одиночного фильтра — на рис. 3.50.

Каждый канал состоит из пяти однотипных фильтров (рис. 3.50). Центральная частота и добротность каждого фильтра целиком зависят от подключенных навесных компонентов (два конденсатора и резистор определенных номиналов). Диапазон управления каждым фильтром разделен на 11 уровней: 5 уровней усиления, 5 уровней ослабления и уровень 0 дБ (без усиления).

Уровни регулировки следующие: 2,7; 5,5; 8,4; 11,6; 15,0 дБ.

Очень важно отметить, что разным уровням регулировки соответствует разная добротность (в оригинальной документации Q-фак-

тор) одиночных фильтров, а значит, и разная тембровая окраска. Поэтому возможно использовать не только собственные усилительные качества фильтра, но еще и управлять частотной характеристикой (варьировать АЧХ с помощью способа «весовых коэффициентов»), дополнительно ослабляя сигнал на выходе. Для этого (рис. 3.50) каскад разделен на две части: boost и cut. Коэффициенты передачи каскадов задаются программно, и об этом мы сейчас поговорим.

Расположение выводов микросхемы ТЕА6360 показано на рис. 3.51, а название выводов — в табл. 3.27.

Таблица 3.27. Назначение выводов микросхемы

| Символ | Вывод | Описание |

| V, | 1 | Вход сигнала левого канала (LEFT) |

| F1LA | 2 | Вывод А фильтра 1 LEFT (f = 2,95 кГц) |

| - | 3 | Не используется |

| F1LB | 4 | Вывод В фильтра 1 LEFT (f = 2,95 кГц) |

| F2LA | 5 | Вывод А фильтра 2 LEFT (f = 12 кГц) |

| F2LB | 6 | Вывод В фильтра 2 LEFT (f = 12 кГц) |

| F3LA | 7 | Вывод А фильтра 3 LEFT (f = 790 Гц) |

| F3LB | co | Вывод В фильтра 3 LEFT (f = 790 Гц) |

| F4LA | 9 | Вывод А фильтра 4 LEFT (f = 205 Гц) |

| F4LB | 10 | Вывод В фильтра 4 LEFT (f = 205 Гц) |

| F5LA | 11 | Вывод А фильтра 5 LEFT (f = 59 Гц) |

| F5LB | 12 | Вывод В фильтра 5 LEFT (f = 59 Гц) |

| V0, | 13 | Выход сигнала левого канала (LEFT) |

| vp | 14 | Вывод пиания |

| SDA | 15 | Линия SDA шины I2C |

| SCL | 16 | Линия SCL шины I2C |

| GND2 | 17 | Общий провод (шина I2C) |

| MAD | 18 | Задание slave-aflpeca |

| GND1 | 19 | Аналоговая «земля» |

| v„ | 20 | Выход сигнала правого канала (RIGHT) |

| F5RB | 21 | Вывод В фильтра 5 RIGHT (f = 59 Гц) |

| F5RA | 22 | Вывод А фильтра 5 RIGHT (f = 59 Гц) |

| F4RB | 23 | Вывод В фильтра 4 RIGHT (f = 205 Гц) |

| F4RA | 24 | Вывод А фильтра 4 RIGHT (f = 205 Гц) |

| F3RB | 25 | Вывод В фильтра 3 RIGHT (f = 790 Гц) |

| F3RA | 26 | Вывод А фильтра 3 RIGHT (f = 790 Гц) |

| F2RB | 27 | Вывод В фильтра 2 RIGHT (f = 12 кГц) |

| F2RA | 28 | Вывод А фильтра 2 RIGHT (f = 12 кГц) |

| F1RB | 29 | Вывод В фильтра 1 RIGHT (f = 2,95 кГц) |

| [ | 30 | Не используется i |

| F1RA | 31 | Вывод А фильтра 1 RIGHT (f = 2,95 кГц) |

| 32 | Вход сигнала правого канала (RIGHT) |

Данные для микросхемы ТЕА6360 передаются по шине I2C в одну сторону.

Структура управляющего пакета данных представлена на рис. 3.52. Такая структура нам знакома, поэтому остается без дополнительных комментариев. Slave-адрес задается комбинацией 1000 0100, когда на выводе 18 присутствует низкий уровень, и комбинацией 1000 0110, когда на выводе 18 — высокий уровень. Субадрес определяет номер фильтра, которому предназначаются данные. Блок DATA — данные по настройке фильтра.

Возможные комбинации данных, содержащихся в субадресе, приведены в табл. 3.28.

Таблица 3.28

| Функция | Субадрес | DATA | |||||||

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | ||

| Фильтр 1/откл. | 00000000 | DEF | 1В2 | 1В1 | 1В0 | 0 | 1С2 | 1С1 | 1С0 |

| Фильтр 2 | 00000001 | 0 | 2В2 | 2В1 | 2В0 | 0 | 2С2 | 2С1 | 2С0 |

| Фильтр 3 | 00000010 | 0 | ЗВ2 | ЗВ1 | ЗВО | 0 | ЗС2 | ЗС1 | ЗСО |

| Фильтр 4 | 00000011 | 0 | 4В2 | 4В1 | 4В0 | 0 | 4С2 | 4С1 | СО |

| Фильтр 5 | 00000100 | 0 | 5В2 | 5В1 | 5В0 | 0 | 5С2 | 5С1 | 5С0 |

Примечания.

• Если вслед за передачей субадреса будет осуществляться передача более одного блока DATA, субадрес будет автоматически инкрементиро- ваться.

• Обозначения в блоке DATA: 1-я цифра означает номер фильтра (1...5), буква обозначает принадлежность данных (boost или cut), 2-я цифра (0...2) — порядок бита. Например, 1В1 означает «1-й фильтр, boost каскад, бит 1».

• Бит DEF отключает или включает эквалайзер. При установке DEF = 0 все фильтры подключены и работают; при установке DEF = 1 сигнал поступает непосредственно со входа на выход с коэффициентом передачи 0 дБ.

Возможные комбинации boost и cut уровней приведены в табл. 3.29 (boost) и табл. 3.30 (cut).

Таблица 3.29

| Позиция | пВ2 | пВ1 | пВО |

| шаг 0 / 0 дБ | 0 | 0 | 0 |

| шаг 1 / 2,7 дБ | 0 | 0 | 1 |

| шаг 2 / 5,5 дБ | 0 | 1 | 0 |

| шаг 3/8,4 дБ | 0 | 1 | 1 |

| шаг 4 / 11,6 дБ | 1 | 0 | 0 |

| шаг 5/ 15,0 дБ | 1 | 0 | 1 |

| шаг 5/15,0 дБ | 1 | 1 | 0 |

| шаг 5/15,0 дБ | 1 | 1 | 1 |

Таблица 3.30

| Позиция | пС2 | пС1 | пСО |

| шаг 0 / 0 дБ | 0 | 0 | 0 |

| шаг 1 /-2,7 дБ | 0 | 0 | 1 |

| шаг 2 / -5,5 дБ | 0 | 1 | 0 |

| шаг 3/-8,4 дБ | 0 | 1 | 1 |

| шаг 4/-11,6 дБ | 1 | 0 | 0 |

| шаг 5/-15,0 дБ | 1 | 0 | 1 |

| шаг 5/-15,0 дБ | 1 | 1 | 0 |

| шаг 5/-15,0 дБ | 1 | 1 | 1 |

Чуть раньше было сказано о «весовых коэффициентах» и о разном характере тембровой окраски в связи с этим. Вариантов может быть много, и тут для читателя открывается широкое поле для экспериментальной проверки, экспериментального нахождения наилучших вариантов. Разработчики микросхемы рекомендуют применять три варианта — с переменным Q-фактором (табл. 3.31), с постоянным Q-фактором (табл. 3.32) и квази-постоянным Q-фактором (табл. 3.33).

Таблица 3.31

| Позиция | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | Примечание |

| X | пВ2 | пВ1 | пВО | X | пС2 | пС1 | пСО | ||

| +5 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | (+5) + (-0) = +5 |

| +4 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | (+4) + (-0) = +4 |

| +3 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | (+3) + (-0) = +3 |

| +2 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | (+2) + (-0) = +2 |

| +1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | (+1) + (-0) = +1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | (+0) + (-0) = 0 |

| -1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | (+0) + (-1) = -1 |

| -2 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | (+0) + (-2) = -2 |

| -3 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | (+0) + (-3) = -3 |

| -4 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | (+0) + (-4) = -4 |

| -5 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | (+0) + (-5) = -5 |

| Таблица 3.32 | |||||||||

| Позиция | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | Примечание |

| X | пВ2 | пВ1 | пВО | X | пС2 | пС1 | пСО | ||

| +5 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | (+5) + (-0) = +5 |

| +4 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | (+5) + (-1) = +4 |

| +3 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | (+5) + (-2) = +3 |

| +2 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | (+5) + (-3) = +2 |

| +1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | (+5) +(-4) = +! |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | (+0) + (-0) = 0 |

| -1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | (+4) + (-5) = -1 |

| -2 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | (+3) + (-5) = -2 |

| -3 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | (+2) + (-5) = -3 |

| -4 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | (+1) + (-5) = -4 |

| -5 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | (+0) + (-5) = -5 |

Таблица 3.33

| Позиция | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | Примечание |

| X | пВ2 | пВ1 | ПВО | X | пС2 | пС1 | пСО | ||

| +5 | 0 | ! | 0 | 1 | 0 | 0 | 0 | 0 | (+5) + (-0) = +5 |

| +4 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | (+5) + (-1) = +4 |

| +3 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | (+3) + (-2) = +3 |

| +2 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | (+4)+ (-2) = +2 |

| +1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | (+3) + (-2) = +1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | (+0) + (-0) = 0 |

| -1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | (+2) + (-3) = -1 |

| -2 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | (+2)+ (-4) = -2 |

| -3 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | (+2) + (-5) = -3 |

| -4 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | (+1) + (-5) = -4 |

| -5 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | (+0) + (-5) = -5 |

Данные, необходимые для проектирования, приведены в табл. 3.34.

На рис. 3.53 приведена частотная характеристика микросхемы при максимальном усилении (boost).

Микросхема выпускается в 32-выводном корпусе SOT232 и SOT287. Рекомендуемое исполнение входных и выходных цепей показано на рис. 3.54.

Таблица 3.34

| Параметр технических условий | Символ | Мин. | Норма | Макс. | Ед. изм. |

| Напряжение питания | Vp | 7 | 8,5 | 13,2 | В |

| Ток потребления | •Р | - | 24,5 | - | мА |

| Максимальный уровень выходного сигнала | Vo | 1,1 | - | - | В |

| Рабочая температура | ^amb | -40 | - | +85 | •с |

| Температура хранения | Tstg | -40 | - | +150 | •с |

| Входное сопротивление (выводы 1 и 32) | Ri | 1 | - | - | МОм |

| Выходное сопроивление (выводы 13 и 20) | Ro | - | 100 | - | Ом |

| Полоса пропускания по уровню -1 дБ | В | 0 | - | 20 000 | Гц |

| Общие гармонические искажения: —V0 =1,1 В; 0 дБ -V0'= 0,1 В; 0 дБ -V„= 1,1 В; +15 дБ -V0 = 0,1 В;+15 дБ -V0 = 0,1 В;-15 дБ | THD | - | 0,2 0,05 0,5 0,1 0,2 | 0,5 0,2 1,0 0,3 0,5 | % |

| Напряжения шума на выходе (среднеквадратическое значение): 0 дБ (все фильтры) +15 дБ (все фильтры) -15 дБ (все фильтры) | VN | - | 23 70 23 | 46 140 46 | мкВ |

| Q-фактор при усилении: Ю дБ 12 дБ 15 дБ | Q | 0,1 0,1 0,1 | - | 1,2 1,4 1,8 | |

| Отклонение параметров фильтров от расчетных | AR.O. | - | - | ±4 | % |

Литература:

Б. Ю. Семенов, «ШИНА 12С В РАДИОТЕХНИЧЕСКИХ КОНСТРУКЦИЯХ» ,Москва СОЛОН-Р 2002

0 коммент.:

Отправить комментарий