Как Вы уже успели заметить, уважаемый читатель, интерфейс I2C требует мощной программной поддержки, которая немыслима без использования современных однокристальных микроконтроллеров. Являясь идеологом данной шины, фирма Philips выпускает на рынок семейство однокристальных МК структуры MCS-51, поддерживающих аппаратно I2C. Другая известная фирма, имеющая право использовать наименование «I2C» в своей продукции — Microchip, — также выпускает ряд однокристальных микроконтроллеров с описываемым интерфейсом.

Существуют микроконтроллеры и других фирм, также аппаратно поддерживающие данный интерфейс. В этой книге мы не будем рассматривать подробно архитектуру микроконтроллеров типов MCS-51 и PIC. Особенности данных архитектур описаны в многочисленной литературе [33—43], имеются материалы и необходимое бесплатное программное обеспечение в сети Интернет. Возможно, данная тема станет предметом последующих книг серии «просто и доступно». А в рамках этой книги мы сделаем блиц-обзор номенклатуры МК, поддерживающих интерфейс I2C и расскажем об общих принципах работы с ним в МК архитектуры MCS-51.

Подробности о работе с ГС в микроконтроллерах архитектуры Р1С приведены в фирменной документации [38—40, 42]. Эта документация переведена на русский язык, и при необходимости ее можно получить в сети Интернет по адресу: http://www.microchip.ru.

Фирма Microchip выпускает следующие микроконтроллеры архитектуры PIC, оснащенные интерфейсом ГС:

PIC14000, PIC16C62A, PIC16CR62, Р1С16С62В, PIC16C63, PIC16C63A, PIC16CR63, PIC16C64A, PIC16C64A, PIC16CR64, Р1С16С65А, Р1С16С65В, PIC16CR65, Р1С16С66, Р1С16С67, PIC16C717, Р1С16С72, PIC16C72A, PIC16CR72, Р1С16С73А, PIC16C73B, PIC16C73C, PIC16CR73C, PIC16C74A, PIC16C74B, PIC16C74C, PIC 16CR74C, PIC16C76, PIC16C76A, P1C16CR76A, Р1С16С77, PIC16C77A, P1C16CR77A, PIC16C770, PIC16C771,

PIC16C773, PIC16C774, PIC16F872, PIC16F873, PIC16F874, PIC16F876, PIC16F877, Р1С16С923, PIC16C924, PIC17C752, PIC17C756, PIC17C756A, PIC17C762, PIC17C766, PIC18C242, PIC 18C442, PIC18C252, PIC18C452.

Сведения о возможностях приведенных микроконтроллеров вы сможете получить непосредственно с сайта фирмы Microchip в Интернете (http://www.microchip.com) или заглянув в документ [41].

Рассмотрим теперь (чуть более подробно) предложение фирмы Philips. Те читатели, кто хоть немного имели дело с микроконтроллерами, знают, что архитектура MCS-51, предложенная Intel в начале 80-х годов XX века, до сих пор остается популярной и у профессиональных разработчиков, и у радиолюбителей. Микроконтроллеры на ее основе в мире выпускает множество фирм. Широка номенклатура МК по своим возможностям, по оснащенности периферийными устройствами, по конструктивным исполнениям. Опубликовано большое количество литературы (в том числе на русском языке), рассказывающей о приемах работы с MCS-51, о программировании, отладке программ и т. д. Если читатель имеет теоретические знания и практический опыт работы с данным типом МК, то он моментально разберется в работе интерфейса I2C. Но если о существовании таких микроконтроллеров читатель лишь наслышан или узнал о них только из этой книги, необходим начальный «ликбез». Чтобы чтение этой главы не стало бесполезным, рекомендуется вначале ознакомиться, например, с изданием [43] и лишь затем продолжать изучение этой книги. Вполне возможно, что читателя вообще не заинтересуют приемы работы с I2C на аппаратном уровне микроконтроллера. Если это так, можно перелистать несколько страниц и перейти к чтению последней — пятой — главы данной книги, где приводятся примеры практических конструкций. Вообще нужно отметить, что несложные практические конструкции, в которых нет необходимости использовать режим multi-master, вполне обойдутся без специализированного ГС аппаратного интерфейса. Интерфейс master-устройства, как мы увидим далее в практической части, можно без труда организовать и про1раммно. Но если все же читателю понадобятся более сложные шинные структуры, без изучения аппаратных интерфейсов, встроенных в МК, ему едва ли удастся обойтись.

б) 3,5...24 МГц;

в) 3,5...30 МГц;

• диапазоны рабочей температуры:

а) 83С552хВх: 0 ... +70 °С;

б) 83C552xFx: -40 ... +85 °С (максимальная частога 24 МГц);

в) 83С552хНх: -40 ... f 125 X (максимальная частота 16 МГц);

• корпуса PLCC68 (SOT188-2) и QFP80 (SOT318-2).

На рис. 4.1 приведена блок-схема структуры данной серии микроконтроллеров. Выполнение портом прямой или альтернативной функции задается соответствующим регистром конфигурации внутри МК.

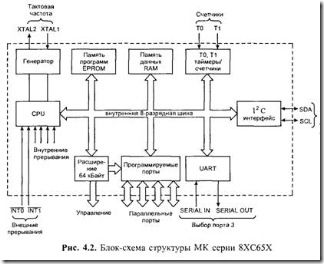

На рис. 4.2. приведена блок-схема структуры МК серии 8ХС65Х. Микросхема выпускается в корпусах DIP40 (SOT 129-1), PLCC44 (SOT 187-2), QFP44 (SOT3Q7-2).

Эта серия идеально подойдет для использования в составе малогабаритной техники, имеющей невысокую стоимость. Главное преимущество МК этой серии — сокращенное число внешних выводов. МК изготавливаются по специальной КМОП технологии, разработанной Philips. В своем составе МК этой серии имеют:

• 83С751 -- 2-кбайтовый ROM;

• 87с751 - 2-кбайтовый EPROM.

В структуре МК предусмотрено энергозависимое read/write ОЗУ емкостью 64 байтов х 8, 19 линий ввода-вывода, счетчик/таймер с ав-

• обеспечение арбитража между master-устройствами для предотвращения возможных шинных конфликтов и потери данных;

• синхронизация по линии SCL, позволяющая совмещать устройства с разными скоростями обмена данными, а также пользоваться механизмом квитирования для приостановления или продолжения передачи данных по шине;

• шина ГС может использоваться для целей диагностики внутреннего состояния микроконтроллера.

При работе с шиной I2C выходные сигналы (output latches) выводов портов Р1.6 и Р1.7 должны быть установлены в состояние «1». Шина I2C представлена в микроконтроллерах несколькими регистрами. Регистр статуса (status register) — S1STA (адрес 09h) — отражает состояние шины. Имеются также управляющий регистр (control register) — SI CON (адрес 98h). регистр данных (data register) — SI DAT (адрес DAh), регистр slave-адреса (slave-address register) — SI ADR (адрес OBh). Назначение внешних выводов: P1.6/SCL, P1.7/SDA.

В зависимости от состояния бита «R/W» обеспечиваются следующие типовые master-операции обмена по шине:

• передача с master-устройства на slave-приемник. Первый байт, переданный master-устройством, является slave-адресом. За ним следует пакет данных, сопровождаемых условием АСК;

• передача данных со slave-устройства на master-приемник. Первый бит (slave-адрсс) традиционно передается master-устройст- вом и подтверждается АСК от slave-aooneirra. Затем следуют пакеты данных. Каждый байт подтверждается сигналом АСК. Последний байт сигналом АСК не подтверждается.

Микроконтроллер имеет возможность генерировать условия start, повторный start и stop.

Порт I2C, представленный в данном МК, может работать также и в режиме slave-устройства. В этом случае МК обнаруживает собственный slave-адрсс или общий вызов (general call address). Если обнаружено одно из этих условий, генерируется прерывание. Когда микроконтроллер хочет захватить шину как master-устройство, аппаратные средства I2C ожидают освобождение шины другими

устройствами, работающими на шине. В случае проигрыша (потери) арбитража аппаратные средства I2C немедленно переходят к slave-pe- жиму.

Далее рассмотрим особенности оперирования с шиной I2C в данном МК. Интерфейсные выводы оснащены входными фильтрами, совместимыми по уровням со стандартными сигналами I2C шины. Если входное напряжение на шине менее 1,5 В, это интерпретируется схемой как логический «О», если напряжение более 3,0 В — логическая «1». Входные сигналы синхронизируются с внутренней тактовой частотой (fosc/4). Выходные транзисторы, подключаемые к внешним pull-up резисторам, не имеют защитных диодов, один из выводов которых традиционно подключается к шине питания VDD. Поэтому, во-первых, возможно использование на шине напряжений, отличных от 5 В, а во-вторых, в случае отключения питания микроконтроллера шина все равно останется работоспособной.

Регистр slave-адреса (S1ADR) является специализированным регистром, в который загружается 7-разрядный slave-адрес. Обратите внимание: slave-адрес можно задавать в любой комбинации битов. Для активизации общего вызова (general call address) необходимо установить младший бит регистра SI ADR (именуемый GC).

Компаратор сравнивает полученный 7-разрядный slave-адрес с собственным slave-адресом, содержащимся в регистре S1ADR, а также идентифицирует общий вызов. Если обнаруживается совпадение, устанавливаются биты в регистре статуса и генерируется прерывание.

Регистр данных (S1DAT) является 8-разрядным регистром, в который помещаются данные для передачи или осуществляется прием данных. Сдвиг регистра S1DAT при оперировании осуществляется справа налево: первым передается бит 7 (MSB). Первый принятый бит размещается в MSB.

Генератор сигнала SCL обеспечивает шину тактовым сигналом в случае работы интерфейса в master-режиме передачи или получения данных. Частота SCL сигнала может программироваться и зависит от частоты тактового сигнала МК (fosc) либо от времени переполнения таймера 1. Генератор сигнала SCL автоматически отключается при переходе интерфейса в slave-режим. Тактирующие импульсы имеют скважность 50%, если не осуществляется синхронизация с другими устройствами.

Блок синхронизации и управления генерирует синхросигналы для обеспечения обработки потока данных. Этот логический блок обеспечивает импульсами сдвига регистр S1DAT, компаратор сравнения slave-адреса, генерирует и обнаруживает состояния Start, Stop, генерирует сигнал АСК, управляет переключением master- и slave-режимов, имеет возможность запросить прерывание, контролирует состояние I2C шины.

Регистр управления S1CON используется микроконтроллером для выполнения следующих функций: запуска и перезапуска последовательной передачи, прекращения последовательной передачи, задания скорости передачи (bit rate), распознавания адреса, фиксации АСК.

Декодер статуса преобразует биты регистра состояния в 5-разрядный код. Этот код уникален для каждого состояния шины I2C. Он может использоваться для генерации адресов подпрограмм, с помощью которых осуществляется обработка возникающих ситуаций (выделяется 26 кодов). Код состояния помещается в регистр состояния и остается неизменным, пока флаг состоявшегося прерывания не будет очищен (естественно, при помощи соответствующих команд). Три младших бита регистра статуса S1STA всегда остаются нулями.

Блок-схема интерфейса I2C в микроконтроллерах 8ХС552 приведена на рис. 4.3.

Поговорим теперь подробнее о четырех названных регистрах (S1ADR, S1DAT, S1CON, S1STA), с помощью которых осуществляется управление шиной.

Структура регистра slave-адреса показана на рис. 4.4.

Процессор может непосредственно адресовать этот регистр, помещать в него данные и читать их. Содержание этого регистра игнорируется в режиме master, а в режиме slave он обязательно должен быть загружен необходимыми данными.

Структура регистра данных приведена на рис. 4.5.

Процессор может непосредственно адресовать этот регистр, помещать в него данные и читать их, но только тогда, когда не происходит процесса передачи (приема) байта. Данные в регистре S1DAT остаются устойчивыми, пока установлен флаг SI в регистре S1CON.

На рис. 4.6 показана схема фиксации данных в регистре S1DAT. Вместе с ячейкой АСК формируется 9-разрядный сдвиговый регистр, бит АСК задается аппаратно без обращения к центральному процессору. Данные сдвигаются при положительных перепадах сип-

хронизиругощих импульсов, бит ЛСК передается на шину в течение 9-го синхронизирующего импульса. Имеется также буфер BSD7. данные из которого сдвигаются по отрицательному перепаду синхроимпульса SCL. Когда центральный процессор записывает данные в S1DAT, бит 7 данных оказывается в ячейке BSD7 и он первым будет передан на шину. После прохождения 9 импульсов SCL данные в регистре S1DAT не изменятся (если осуществлена их передача).

Структура управляющего регистра приведена на рис. 4.7.

Процессор может непосредственно адресовать этот 8-разряднып регистр по операциям чтения и записи. Регистр имеет несколько битов с уникальными названиями, которые используются в следующих случаях:

• бит STO очищается, когда возникает условие Stop; этот бит также очищается, когда F.NS 0;

• бит ENS1 — бит разрешения работы I2C шины; когда ENS1 =■■■■ О, на линиях SDA и SCL присутствуют высокие уровни сигналов, линии не реагируют на внешние сигналы; интерфейс находится в неадресуемом slave-состоянии, выводы Р 1.6 и Р 1.7 можно использовать как обычные порты ввода-вывода. Когда ENS1 = 1. выходные уровни (port latches) портов PI.6 и PI.7 должны быть установлены в состояние с высоким уровнем. Бит ENS1 нельзя использовать для временной приостановки обмена по шине I2C,

так как в противном случае (при сбросе ENS1) состояние активизации шины будет потеряно. Для этих целей задействуется флаг АА;

• бит STA — флаг START. Бит STA устанавливается в «1» в случае необходимости перехода порта в master-режим. Аппаратные средства порта проверяют состояние линий SDA и SCL, генерируют условие Start в случае свободной шины. Если шина не свободна, порт ждет появления на шине условия Stop и генерирует условие Start. Если бит STA будет установлен повторно после того, как получено или передано несколько байтов, будет сгенерировано повторное условие Start. Бит STA может также устанавливаться в режиме slave-порта. Состояние STA = 0 — сброс бита STA, отсутствие генерации условия Start, повторения условия Start;

• бит STO — флаг STOP. Бит STO устанавливается в «1» в master-режиме, когда по шине ГС необходимо передать условие Stop. Когда условие Stop появилось на шине, бит STO будет очищен. В случае работы в slave-режиме бит STO может быть использован для исправления ошибок. В этом случае условие Stop на шину передано не будет, но аппаратные средства порта I2C станут вести себя так, как будто условие Stop получено, и переключат порт в неадресуемое slave-состояние. Бит STO автоматически очистится. Когда STO = 0, условие Stop не передается;

• бит SI устанавливается в случае генерации прерывания от порта ГС. Если SI = 1 и если регистры ES1 и ЕА (interrupt enable registers) — регистры прерываний (не рассматриваются нами в данной книге) — соответствующим образом сконфигурированы, будет происходить генерация прерываний от порта I2C;

• бит АА — флаг подтверждения АСК. Если бит АА = 1, будет сгенерирован сигнал АСК в случае получения собственного slave-адреса, общего адреса запроса (general call address), при получении байта данных в master-режиме, при получении байта данных в slave-режиме. Если АА = 0, АСК не будет сгенерирован;

• биты CRO, CR1, CR2 -- биты задания тактовой частоты SCL в master-режиме. Состояние битов и значение генерируемой так-

товой частоты приведены в табл. 4.1. В режиме slave-порт I2C автоматически синхронизируется с любой тактовой частотой в пределах 100 кГц.

Таблица 4.1

| CR2 | CR1 | CR0 | Тактовая частота f^, | кГц | |

| 6 МГц | 12 МГц | 16 МГц | |||

| 0 | 0 | 0 | 23 | 47 | 63 |

| 0 | 0 | 1 | 27 | 54 | 71 |

| 0 | 1 | 0 | 3! | 63 | 83 |

| 0 | 1 | 1 | 37 | 75 | 100 |

| 1 | 0 | 0 | 6,25 | 12,5 | 17 |

| 1 | 0 | 1 | 50 | 100 | - |

| 1 | 1 | 0 | 100 | - | - |

| 1 | 1 | 1 | 0,25 < 62,5 | 0,5 < 62,5 | 0,67 < 56 |

Структура регистра статуса приведена на рис. 4.8.

Регистр статуса доступен только по операции чтения. Три младших бита (2...0) всегда остаются нулевыми, а биты SC4...SC0 содержат код состояния. Особая ситуация, связанная с выдачей кода F8h, будет описана далее.

Порт I2C может обеспечивать четыре основных режима:

• Master Transmitter (master-передатчик);

• Master Receiver (master-приемник);

• Slave Receiver (slave-приемник);

• Slave Transmitter (slave-передатчик).

Рассмотрим подробнее эти режимы применительно к описываемому микроконтроллеру.

Master Transmitter. В этом режиме master-устройство передает данные к slave-абоненту. Прежде чем перевести порт микроконтрол- лера в режим master transmitter, необходимо провести инициализацию в регистре S1COM согласно рис. 4.9, а также задать комбинацию бит CR0...CR2 в соответствии с предполагаемой скоростью передачи (bit rate). Бит АА может быть либо установлен, либо сброшен. Если бит АА сброшен, порт не сможет при приеме подтвердить собственный slave-адрес или general call address с другого master-устройства, желающего стать «хозяином» шины.

Итак, как только шина становится свободной, порт I2C генерирует условие Start, после чего в регистре статуса S1STA устанавливается код 08h, устанавливается флаг SI. Этот код может быть использован для обработки прерывания. По прерыванию может быть загружен регистр S1DAT slave-адресом и битом направления данных R/W — в данном случае W. Бит SI в регистре S1CON должен быть сброшен, прежде чем будет возобновлена передача. Когда slave-эд- рес и бит направления были переданы, получен сигнал АСК, флаг SI снова устанавливается. Регистр статуса в данном случае может содержать варианты кодов: 18h, 20h, 38h — в случае разрешения работы только в качестве master-абонента или 68h, 78h, BOh — в случае разрешения slave-режима (бит АА установлен в «1»), Действия, которые нужно предпринимать при получении данных кодов, приведены в табл. 4.2.

После выполнения условия «повторный Start» генерируется код 1 Oh, производится загрузка регистра S1DAT slave-адресом с условием R.

Master Receiver. В этом режиме данные поступают от slave-nepe- датчика к master-приемнику. Инициализация производится точно так же, как и в предыдущем случае. После передачи условия Start программа обработки прерывания должна загрузить регистр S1DAT 7-разрядным slave-адресом и битом R направления данных. После этого могут быть продолжены операции обмена. После передачи

slave-адреса, получения сигнала АСК устанавливаются коды в регистре состояния. Их может быть несколько: 40h, 48h, 38h — для режима master или 68h, 78h, BOh — в случае разрешения slave-режима (бит АА = 1). Действия, которые нужно предпринимать при получении кодов, приведены в табл. 4.3.

После выполнения условия «повторный Start» генерируется код 10h, производится загрузка S1 DAT slave-адрссом с условием W.

Slave Receiver. В этом режиме микроконтроллер становится slave-устройством и получает данные от master-устройства, располагающегося на шине. Инициализация режима показана на рис. 4.10.

Как уже было сказано ранее, биты CR2...CR0 не воздействуют на скорость приема в slave-режиме. Бит АА должен быть установлен для получения возможности подтверждения собственного slave-ад- реса или general call address. Не забывайте также загружать в регистр S1ADR собственный slave-адрес микроконтроллера.

После инициализации порта он входит в состояние ожидания получения slave-адрсса с битом направления данных W. После получения адреса генерируется прерывание (устанавливается бит SI) и код состояния в регистре статуса. Возможные варианты кодов состояния приводятся в табл. 4.4.

Режим slave может автоматически устанавливаться в случае multi-master организации шины при программном арбитраже (коды 68h и 78h). Обратите внимание: при сброшенном бите АА микроконтроллер может не подтвердить прием собственного slave-адреса или general call address. Таким образом, бит АА можно использовать для временной изоляции порта I2C микроконтроллера от шины.

Slave Transmitter. В этом режиме микроконтроллер в роле slave-устройства передает данные на другое master-устройство. Инициализация производится точно так же, как и в предыдущем примере. После инициализации порт I2C ожидает прием собственного slave-адреса с битом направления данных R. После получения slave-адреса и подтверждения АСК устанавливается бит SI, код в регистре статуса. Возможные комбинации кодов приведены в табл. 4.5.

Существует несколько шинных состояний, называемых исключениями. Они не могут быть четко отнесены к перечисленным выше режимам.

Код F8h указывает на то, что флаг SI не установлен, а также порт ГС не активизирован. Обычно устанавливается в промежутках между генерацией других кодов.

Код 00h указывает на ошибку, произошедшую во время обмена данными по шине I2C. Обычно ошибки связаны с генерацией условий Start и Stop в непредусмотренное время, например, в течение передачи байта slave-адреса, байта данных или условия АСК. Ошибка может быть также вызвана помехой на шине. При обнаружении ошибки устанавливается бит SI.

Чтобы избавиться от состояния ошибки, нужно предпринять следующие действия: установить бит STO и очистить бит SI. Эти действия переведут порт в неадресуемый slave-режим и освободят линии SDA и SCL.

Аппаратные средства порта могут отследить одновременную генерацию условия «повторный Start» от двух master-абонентов. Причем эти условия могут быть сгенерированы как в режимах master receiver, так и master transmitter. Данная ситуация показана на рис. 4.11.

Потеря арбитража отражается в регистре S1STA кодами 38h, 68h, BOh.

Правила написания программного обеспечения также приводятся в документе [33]. Мы не будем останавливаться на них, поскольку не

задавались такой целью. Читатель, пожелавший работать с 1?С интерфейсом на уровне программирования микроконтроллеров со специализированными портами, сделает это самостоятельно.

Таблица 4.2

| Состояние регистров | |||||||

| Код S1STA | Состояние шины I2C | S1DAT | S1CON | Дальнейшие действия | |||

| STA | STO | SI | АА | ||||

| 08h | Передача условия Start | Загрузка slave + W | X | 0 | 0 | X | slave + W будет передан; бит АСК будет получен |

| 10h | Повторная передача условия Start | Загрузка slave + W Загрузка slave + R | X X | 0 0 | 0 0 | X X | Аналогично slave + W будет передан; |

| 18h | slave + W передан, АСК получен | Загрузка байта данных S1DAT неактивен S1 DAT неактивен S1 DAT неактивен | 0 1 0 1 | 0 0 1 1 | 0 0 0 0 | X X X X | Байт данных будет передан; бит АСК будет получен; «повторный Start» будет передан; условие Stop будет передано; флаг ST0 будет сброшен; условие Stop, сопровождаемое условием Start, будет передано; флаг ST0 будет i сброшен |

| 20h | slave + W передан, АСК не получен | Загрузка байта данных S1DAT неактивен S1DAT неактивен S1DAT неактивен | 0 1 0 1 | 0 0 1 1 | о о о о | X X X X | Аналогично предыдущей ситуации |

| 28h | Данные из регистра S1 DAT переданы, АСК получен | Загрузка байта данных S1DAT неактивен S1 DAT неактивен S1DAT неактивен | 0 1 0 1 | 0 0 1 1 | 0 0 0 0 | X X X X | Аналогично предыдущей ситуации |

| 30h | Данные из регистра S1 DAT переданы, АСК не получен | Загрузка байта данных S1DAT неактивен S1DAT неактивен S1DAT неактивен | 0 1 0 1 | 0 0 1 1 | 0 0 0 0 | X X X X | Аналогично предыдущей ситуации |

| 38h | Арбитраж slave + R/W байта данных | S1 DAT неактивен S1 DAT неактивен | 0 1 | 0 0 | 0 0 | X X | Шина освобождается, вводится неадресуемый режим, условие Start будет передано, когда шина освободится |

Таблица 4,3

Таблица 4.4

Окончание таблицы 4.4

| Состояние регистров | |||||||

| Код S1STA | Состояние шины RC | S1CON | Дальнейшие действия | ||||

| S1DAT | |||||||

| STA | STO | SI | АА | ||||

| 90h | general call address принят, АСК возвращен | Чтение данных Чтение данных | X X | 0 0 | 0 0 | 0 1 | Байт данных будет получен; бит, АСК не будет возвращен; байт данных будет получен, АСК будет возвращен |

| Переключение к не адресуемому | |||||||

| slave-режиму; не опознается соб | |||||||

| general call ad | Чтение данных | 0 | 0 | 0 | 0 | ственный slave или общий адрес | |

| 98h | dress принят, | Чтение данных | 0 | 0 | 0 | I | вызова; собственный slave-aflpec |

| АСК не возвра | Чтение данных | 1 | 0 | 0 | 0 | будет распознан; общий вызов бу | |

| щен | Чтение данных | 1 | 0 | 0 | 1 | дет распознан,если бит 0 S1ADR = 1; условие Start будет передано, когда шина освободится | |

| Условие Stop и | S1 DAT неактивен | 0 | 0 | 0 | 0 | ||

| AOh | повторное условие Start получено | S1DAT неактивен S1DAT неактивен S1 DAT неактивен | 0 1 1 | 0 0 0 | 0 0 0 | 1 0 1 | Аналогично предыдущей ситуации |

Таблица 4.5

| Состояние регистров | |||||||

| Код St STA | Состояние шины PC | S1CON | Дальнейшие действия | ||||

| S1DAT | |||||||

| STA | STO | SI | АА | ||||

| A8h | slave + R принят, | Загрузка данных | X | 0 | 0 | 0 | Последний байт данных будет пе |

| АСК возвращен | Загрузка данных | X | 0 | 0 | 1 | редан и бит АСК будет получен | |

| Арбитраж slave + | |||||||

| BOh | R/W master, slave + R принят, АСК возвращен | Загрузка данных Загрузка данных | X X | 0 0 | 0 0 | 0 1 | Аналогично предыдущей ситуации |

| B8h | Байт данных из S1DAT передан, АСК возвращен | Загрузка данных Загрузка данных | X X | 0 0 | 0 0 | 0 1 | Аналогично предыдущей ситуации |

| Переключение к не адресуемому | |||||||

| slave-режиму; не опознается соб | |||||||

| Байт данных из St DAT передан, АСК не возвращен | SI DAT неактивен St DAT неактивен S1DAT неактивен S1DAT неактивен | 0 0 1 1 | 0 0 0 0 | 0 0 0 0 | 0 1 0 1 | ственный slave или общий адрес вызова; собственный slave-адрес | |

| con | будет распознан; общий вызов будет распознан, если бит 0 S1ADR = 1; условие Start будет передано, когда шина освободится | ||||||

| Прошлый байт из | S1 DAT неактивен | 0 | 0 | 0 | 0 | ||

| C8h | St DAT передан (АА = 0); АСК | S1 DAT неактивен S1DAT неактивен | 0 1 | 0 0 | 0 0 | 1 0 | Аналогично предыдущей ситуации |

| возвращен | S1DAT неактивен | 1 | 0 | 0 | 1 |

Литература:

Б. Ю. Семенов, «ШИНА I2С В РАДИОТЕХНИЧЕСКИХ КОНСТРУКЦИЯХ» ,Москва СОЛОН-Р 2002

0 коммент.:

Отправить комментарий