Операнды – двоичные вектора (коды). У кодов все разряды равнозначны (знаковых разрядов нет).

Необходимо построить комбинационный преобразователь, реализующий набор функций С(1: n) := А(1: n) * В(1: n), где * - одна из следующих операций над кодами: конъюнкция, дизъюнкция, инверсия, сложение по модулю два (рисунок 1). Функциональная схема i – го разряда преобразователя представлена на рисунке 2.

Для выполнения набора функций вида А:=А*В необходимо к построенному преобразователю подключить двухступенчатый регистр (рисунок 3).

Далее приводится несколько упрощенных вариантов реализации операций над кодами.

Чтобы реализовать операцию нужно сигнал этой операции yГ закоммутировать на счетный вход соответствующего триггера (i – го разряда регистра А) (рисунок 4).

Схема, выполняющая микрооперации

yÚ : А := А Ú В и

yÙ : A := A Ù B , приведена на рисунке 5.

Таблица1 описывает операцию дизъюнкции.

Таблица1

| At | Bt | At+1 | |

| 0 | 0 | 0 | |

| 0 | 1 | 1 | |

| 1 | 0 | 1 | |

| 1 | 1 | 1 |

Если yÚ = 1 , то yÙ = 0 (так как две микрооперации не могут выполняться над одним и тем же регистром одновременно), следовательно на R-вход триггера подается ноль (R=0), на S-вход подается bi (S = bi ). Если bi =1, то триггер устанавливается в 1, если bi =0, то триггер хранит свое состояние, т.е. ai. Схема работает в соответствии с таблицей 1.

Таблица 2 описывает операцию конъюнкции.

Таблица2

| At | Bt | At+1 | |

| 0 | 0 | 0 | |

| 0 | 1 | 0 | |

| 1 | 0 | 0 | |

| 1 | 1 | 1 |

Если yÙ = 1 , то yÚ = 0 (так как две микрооперации не могут выполняться над одним и тем же регистром одновременно), следовательно на S-вход триггера подается ноль (S=0), на R-вход подается (R =

). При bi =0,

=1, т.е. триггер сбрасывается в ноль. При bi =1,

=0, триггер хранит свое состояние , т.е. ai.

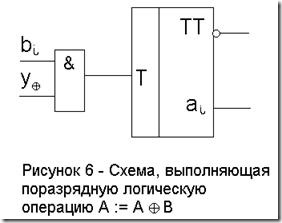

На рисунке 6 изображен i-ый разряд схемы, выполняющей микрооперацию

yÅ : А := А Å В .

Таблица 3 описывает операцию исключающего ИЛИ - сложения по модулю два ( Å).

Таблица3

| At | Bt | At+1 | |

| 0 | 0 | 0 | |

| 0 | 1 | 1 | |

| 1 | 0 | 1 | |

| 1 | 1 | 0 |

При bi =1, ai =1, ai t+1 =0 (триггер переключается);

при bi =1, ai =0, ai t+1 = 1 (триггер переключается);

при bi =0, ai =1, ai t+1 = 1 (триггер не переключается);

при bi =0, ai =0, ai t+1 = 0 (триггер не переключается).

В рассмотренных схемах каждая поразрядная логическая операция реализована одной микрооперацией (выполняется за один такт по соответствующему управляющему сигналу y).

Операция сдвига

1) Логический сдвиг кода. Все разряды кода А участвуют в операции одинаково. Освобождающиеся разряды обычно заполняются нулями. Разряды, выдвигаемые за разрядную сетку, теряются. В отличие от микрооперации сдвига в операции сдвига задается константа сдвига.

Пример. Логический сдвиг кода влево на два разряда:

L3 (011110) = 110000

Циклический сдвиг кода (разновидность логического). Освобождающиеся разряды доопределяются значениями разрядов, выдвигаемых за разрядную сетку:

L3 цикл (011110) = 110011

2) Арифметический сдвиг двоичного числа. Старший (знаковый) разряд числа А в сдвиге не участвует (его значение не изменяется). Информационные разряды, выдвигаемые за разрядную сетку, как правило, теряются. При сдвиге вправо освобождающиеся информационные разряды слова А доопределяются значением знакового разряда. При сдвиге влево освобождающиеся разряды доопределяются нулями.

Пример:

R3 ар (1 001100) = 1 111001;

L3 ар (1 001100) = 1 100 000

Арифметический сдвиг на один разряд использовался в рассмотренных микропрограммах умножения двоичных чисел с фиксированной точкой в дополнительных кодах (сдвиг вправо) и деления двоичных чисел с фиксированной точкой (сдвиг влево).

В качестве примера рассмотрим микропрограмму логического сдвига слова А (рисунок 7). Структурная схема операционного автомата, выполняющего операцию сдвига, представлена на рисунке 8.

Младшие разряды регистра В ( т.е. В(n-k: n), где k=]log2n[ ) определяют константу сдвига. Старший разряд регистра В задает направление сдвига: если В(1) = 1, то сдвиг вправо, иначе – сдвиг влево.

В общем случае константа сдвига может принимать значение, большее, чем n, так как в одном и том же устройстве могут сдвигаться, например, 32-разрядные и 64-разрядные слова.

Ускорение данной операции сдвига возможно за счет использования дополнительных цепей сдвига (на два разряда). Если в регистре А реализованы микрооперации сдвига на два разряда и на один разряд, то слово А можно сдвигать на два разряда, пока счетчик больше двух и только в последнем такте на 1 разряд (если константа сдвига нечетная).

0 коммент.:

Отправить комментарий